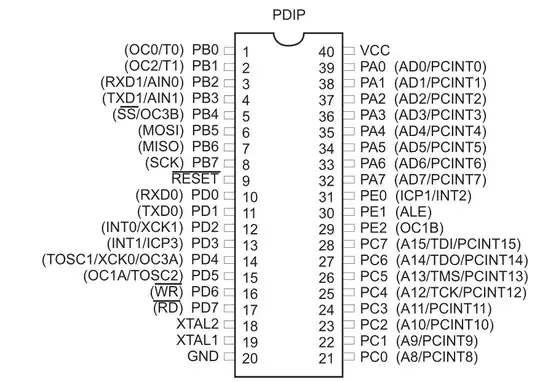

I'm making a board which will host an ATmega 162 microcontroller in PDIP package. Unfortunately, VCC and GND pins are diagonally arranged. From what I've read, the capacitors should be as close to the pins as possible for maximum effect.

Right now, I can see 3 ways to connect the capacitors. Run wires to the capacitors so that they are at equal distance from both pins, place capacitors near ground and run wire to VCC or place capacitors near VCC and run wire to ground. There's always the "none of the above" option too.

How do I make right decision in this case? Or is is irrelevant?