I am dealing with synthesis of verilog sources using Vivado Design Suite 2013.3 tool for the first time.

The behavior of my design is correct as verified by the pre-synthesis simulation.

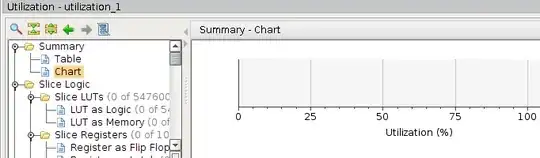

My problem is that once I perform the synthesis, the resulting netlist is empty and this is confirmed by the utilization report which shows that anything has been utilized on the board I previously chose.

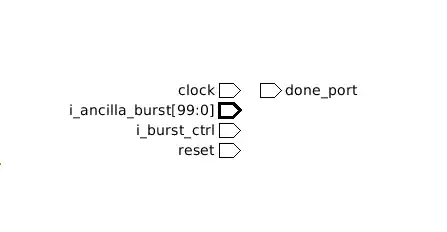

The only thing I can see from the scheme are the ports of the top module of my architecture:

This is the utilization:

I have been told that, since my data source is from outside of my device, I have to set the IOB option in the synthesis settings, but neither the official Xilinx guides are helping me on this.