The speed of the GPIO can be 2-4 times the speed grade of the FPGA itself. The IO blocks of the FPGA, are designed to support higher speed than the FPGA can support. This is because many of these IOs are created to support high speed IOs such as PCIe, USB 3 or even 3 and RapidIO just to mention a few.

Even if your FPGA's maximum clock is 400MHz, you can access IOs at twice that speed using the DDR blocks of the IO or even 4 times that using a QDR block.

It is also possible to serialize and de-serialize the data to/from the IOs, which makes it possible for a low cost FPGA to access high speed interfaces.

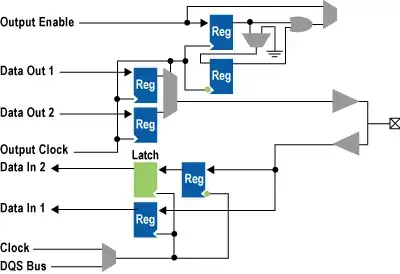

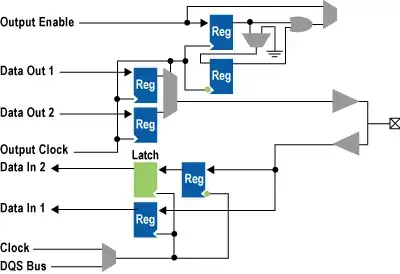

For example Altera Stratix II has the following IO blocks:

I am sure you can find similar description from other FPGA companies as well.

You can take a look at this PDF file from xilinx regarding high speed serial IO capabilities of their FPGAs.

http://www.xilinx.com/publications/archives/books/serialio.pdf

For example, in my last project, we managed to connect and FPGA to PCIe Gen 3 at 8Gb/s even thought the maximum achievable internal speed for the FPGA was about 250MHz. In that project, we used a special PCM module, you can read more about PCIe access support of Xilinx FPGAs at:

http://www.xilinx.com/technology/protocols/pciexpress.htm