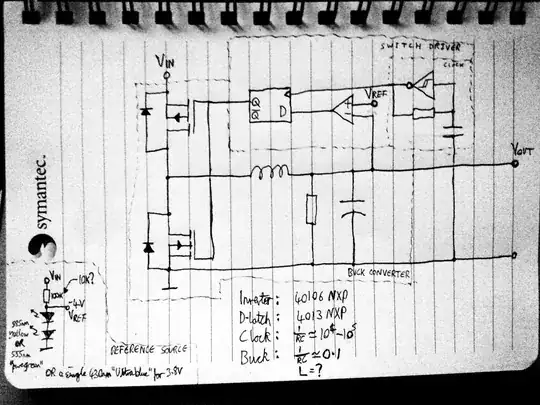

I've been reading up on power electronics lately and as a challenge (and also a learning exercise), designed my first switching power supply - a buck converter in this case.

It is intended to supply 3.5-4.0V (decided by diode reference source) and up to 3A in order to drive some power LEDs with any DC source, ranging from a 5V USB charger up to a 9V PP3 battery. I want an efficient supply, as heating and battery life will be a real issue (otherwise I'd be lazy and use a 7805+diode).

NOTE: I already noticed that I've got the switching logic the wrong way round, I need to either swap the connections into the comparator or use !Q to drive the MOSFETs.

My choice of MOSFETs instead of BJTs was due to the power losses in a BJT, and the thermal issues arising. Is this decision to use MOSFETs over BJTs/IGBTs due to improved efficiency the right call?

Rather than using a PWM chip as many hobbyist forums suggest, I decided to use a comparator/clock/latch combination to rapidly switch between "charging" and "discharging". Is there any particular disadvantage of this approach? The CMOS latch (a D-flip flop) copies data to the outputs on the rising edge of pulses from the clock generator (a CMOS Schmitt inverter + feedback).

The choice of time constants / corner frequencies for the clock and the buck lowpass (10-100kHz and 10Hz respectively) is intended to support the small ripple approximation while also allowing the output capacitor to charge in a reasonable amount of time from power-on. Is this the right set of considerations for deciding the values of these components?

Additionally, how would I go about calculating the value of the inductor? I would assume that it depends upon the typical output current and the lowpass capacitor's value, but I can't quite figure out how.

[edit:]

In the past, I've used the shown MOSFET pair (in addition to software PWM) to create H-bridges for bi-directional, variable speed motor control - and as long as I kept the PWM period much larger than the MOSFET switching time, the power waste from shorting during switching was negligible. In this case though, I'm going to replace the N-mosfet with a Schottky diode since I've never used a Schottky diode before and want to see how they behave.

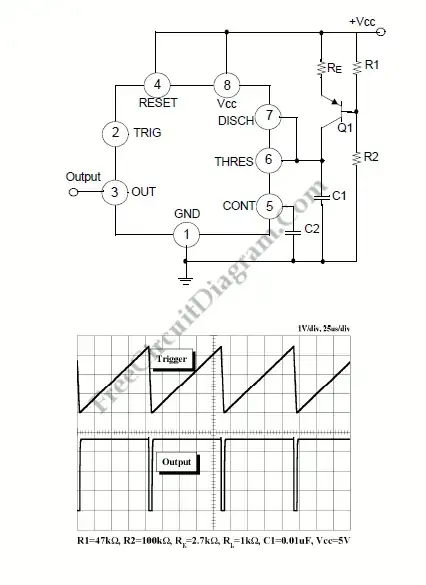

I use a simple inverter+RC combo to provide the clock signal as I don't need a particularly consistent or precise frequency as long as it is considerably higher than the high-cut corner frequency of the buck-boost.

[edit II:]

I built it on a breadboard and to my surprise, it worked straight away without any issues, and at ~92% efficiency (compared to the 94% that I'd calculated from switching/component losses).

Note that I omitted the resistor in the output stage, out of laziness - also I can't quite recall why I put it there in the first place.

I omitted the reverse diode parallel to the P-MOSFET, and also used a 1N5817 Schottky diode (note: 1A rating) in place of the N-MOSFET. It doesn't heat enough for my fingertips to notice. I've ordered a higher-rated diode though for when I assemble the final unit, which will run with full load.

I accidentally blew the LM393 comparator during testing, but an LM358AN took its place straight away without any issues.

As I can't find any decent circuit design+layout/routing software that will run on Arch Linux x64 (or even install, in the case of native Linux software), I've manually layed it out so it probably won't work by the time it's soldered... But that just adds to the "fun" I guess!

Component values used: Clock gen { 1kR, 100nF }; Buck output { 330uH, 47uF }; Input capacitor [not shown] { 47uF }; P-MOSFET { STP80PF55 }; N-MOSFET { Schottky diode instead, 1N5817 - to be replaced with >=3A version }; ICs { 40106 NXP, 4013 NXP, LM358AN }