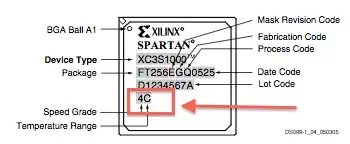

According to Xilinx FPGA product datasheets, the numbers on the 5th line as 4C or 5I stand for speed grade and temperature.I have a XC3S400 with 4C speed grade (4= standard speed, 5= High performance).

I want to know what exactly the standard speed grade means ? Can I relate it to a specific bandwidth? For example assume I want to make a high speed counter and want to use the maximum possible speed driven from a crystal oscillator into GCKx pins. Can I use this 4C marking as a guide for crystal oscillator selection?