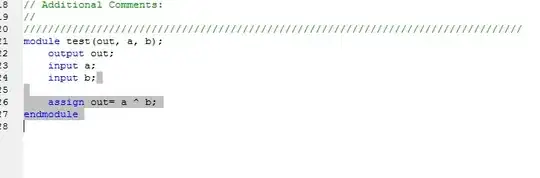

I am very new to FPGA and sorry for this elementary question. I just made a very simple XOR code like this with Webpack ISE to download to XC2S100 ( just for test!) but it does not work.

EDITION1: According to comments, I checked DONE situation after programming and it is in High state. Also added pull down resistors to a and b. Also added a 1KΩ pull down resistor to TMS. Now it works fine but after I restart the device, it does not work any more.It seems the configuration memory is erased after shut down.

1- Obviously this code sythesizes well, and simulation is OK. Then Implemented -> Assigned pins -> re-implemented -> and finally Generated .bit file ( this sequence: )

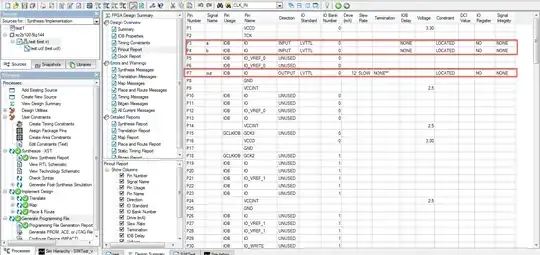

2- I also used the pins that don't require Vref. ( a:P3 , b:P4, out:P7). Here is a screenshot of pin assignment. At the end clicked Save:

3- Then I re-implemented and checked the pins in design summary. All OK:

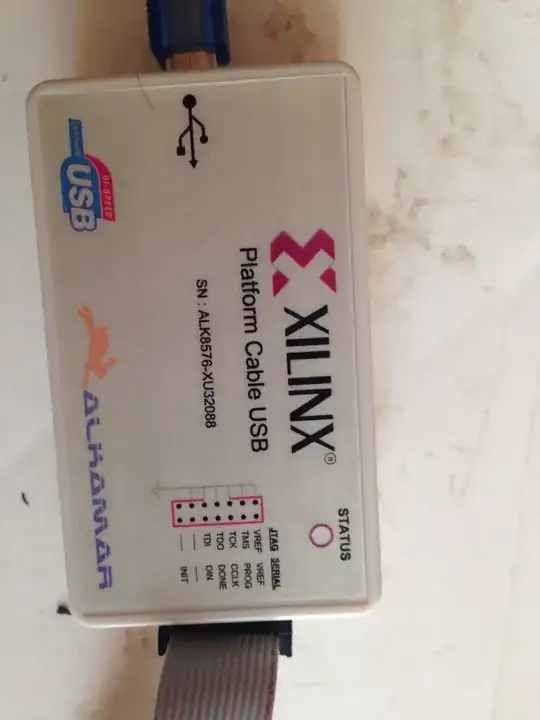

4- I have one of these Alkamar download cables. I connected the pins as recommended and ran iMPACT . It finds the device well and reads its config also well. I was happy when I saw "Program Succeeded " message! but when I connect VCCO voltage (3.3v) to P3(a) or P4(b), nothing happens in P7(out).I double checked everything but of no avail!

What is going wrong there?

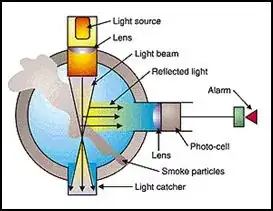

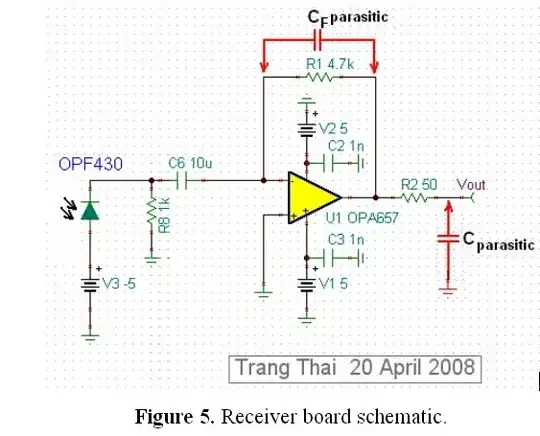

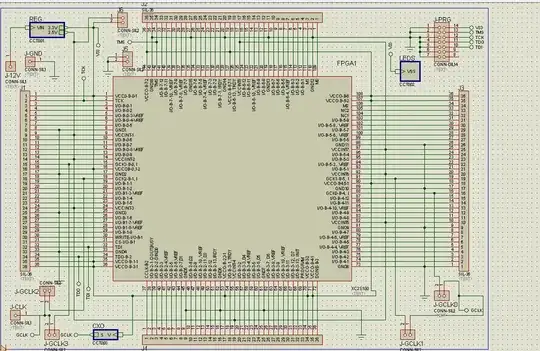

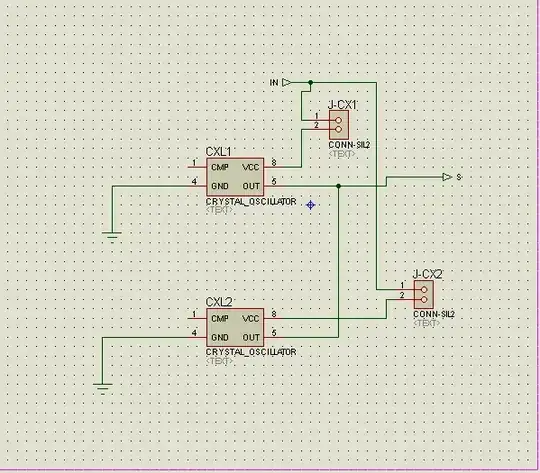

Here is the schematic I use:

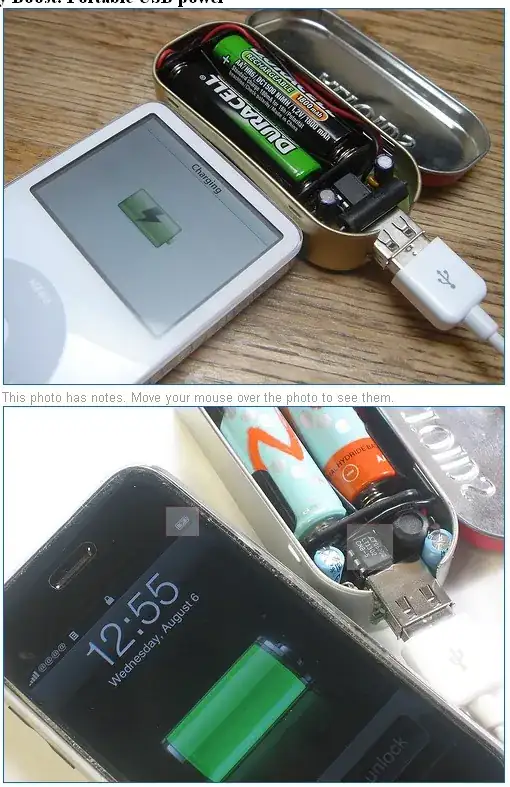

1- Test board:

2- Power Supply:

3- Crystal Oscillator part ( Not used in this test ):

This is the programming cable: