In VHDL simulation, there is a concept of "delta time," which is loosely interpreted as "group of events triggered by the previous delta time." After a change, once all cascading changes have settled, and no more delta time events are generated, the simulation time advances. (Also, simulation time may advance after N delta time events, as there is some upper limit to the length of a cascade.)

In a given process, when is a change to the process sensitivity list triggered? Is it only triggered when the state of a signal is different at one simulation time as compared to the previous simulation time, or can it be triggered as a result of any delta time event? If it is triggered at any delta time, a process may be triggered more than once if there are ephemeral combinatoric logic?

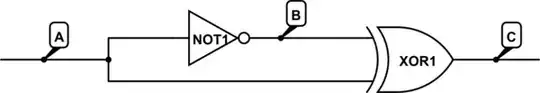

Consider this example:

simulate this circuit – Schematic created using CircuitLab

Let's say we start with steady state A=1, B=0, C=1. Also, let's assume there is no external entity inspecting signal B -- it is purely internal.

Now, introduce a simulation event: A=0.

This will generate an output event for B=1, and an output event for C=0, for the next delta time. At the next delta time, a new output event for C=1 will be generated, and no more events will be generated, so simulation time can advance.

Now, let's say I have a process with C in the sensitivity list. Let's say this process increments a counter each time it is invoked.

Will that counter be incremented twice as a result of A change? That would be the case if delta-time changes provoke/trigger/invoke processes.

Or will that counter be incremented zero times? That would be the case if only simulation-time changes provoke/trigger/invoke processes.

Or is the relation between change-in-A and process-counter undefined? For example, if the simulator (or synthesizer, for hardware,) optimizes the NOT-and-XOR truth table, it will say that C is always 1, but if it doesn't optimize it, it may generate two changes for C and thus trigger the process twice?

Second question: What's the correct word to use for "provoking/triggering/invoking" a process by changing some signal in its sensitivity list?