I am trying to create a custom data type which I am creating in a package using Xilinx ISE 14.5. I am trying to create a generic DEMUX to switch between buses, here is the code of the generic DEMUX:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

use work.CustomDataTypes.all;

entity GenericDEMUX is

-- Ancho del bus de cada salida y número de salidas

generic( busWidth : integer := 4;

channelsNumber : integer := 4

);

Port ( Output : out Matrix(channelsNumber-1 downto 0, busWidth-1 downto 0);

Control : in integer range 0 to channelsNumber-1

);

end GenericDEMUX;

architecture Behavioral of GenericDEMUX is

begin

end Behavioral;

So I created a Package to contain Matrix data type:

CustomDataTypes.vhd:

package CustomDataTypes is

type Matrix is array (natural range<>) of STD_LOGIC_VECTOR (natural range<>);

end CustomDataTypes;

When I do Check Syntax on the Generic DEMUX I get this errors:

ERROR:HDLParsers:164 - "//vboxsrv/datos/Datos/Micro UTN/FPGA/MaquinaEstados/CustomDataTypes.vhd" Line 14. parse error, unexpected NOTCONSTRAINT

ERROR:HDLParsers:3009 - "//vboxsrv/datos/Datos/Micro UTN/FPGA/MaquinaEstados/CustomDataTypes.vhd" Line 35. Package CustomDataTypes does not exist.

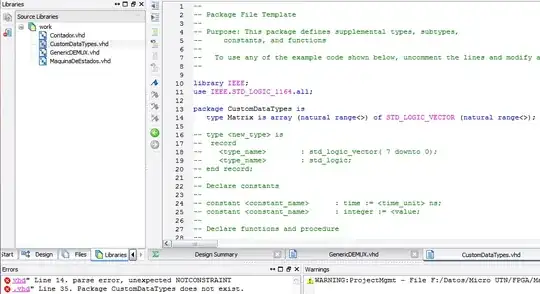

I don't know what parse error, unexpected NOTCONSTRAINT means but I think it could be related to Package CustomDataTypes does not exist. Here is a Screenshot of what my Libraries tab looks like, as you can see CustomDataTypes.vhd is there:

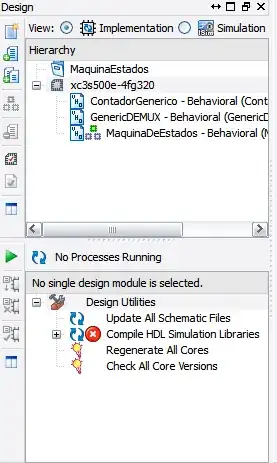

However I don't see it in the design tab:

I tried adding it but it says it already exists.