I think that the simulation can't provide you with the answer to this questions because basic transistors models are developed to be accurate in the forward regions of operations.

The only correct answer may be obtained from building a test circuit and measuring the response of the actual transistor.

In order to give you even approximate theoretical answer (with high degree of confidence), we will need to see the actual internal implementation of the transistor (silicon schematics) - not all transistors are built in the same way, therefore there is no general answer can be given. Manufacturers tend to keep the manufacturing technologies secret, therefore your chances to get a reliable theoretical answer are very low.

I say buy few transistors and go to a lab.

EDIT:

Few folks in the comments suggested that this answer is incorrect because there are no low level Spice models for this transistor. Here are two:

However, even obtaining Bsim3 model for this device does not necessarily means that the simulation will give correct results. At least two reasons for this:

- There is no way to know how accurate your model is

- Even if the model is accurate for the forward biased transistor, these models (to my knowledge) are not required to be accurate for reverse biased devices. This means that there is no one who can give you any guarantees as to the accuracy of the results in the conditions you mentioned.

Have a look at this reference. These guys tried to model trench power MOSFET with custom tailored Bsim3 model. While the accuracy in forward region of operation is good, it is not perfect. And still, no one gives any guarantees as to the accuracy of reverse bias modeling. They also note that there are additional difficulties in applying this model to other topologies of power MOSFETs.

Now, the transistor in question is DMOS, therefore any analysis performed on the model of simplest "logic" transistor will be inherently wrong.

EDIT2:

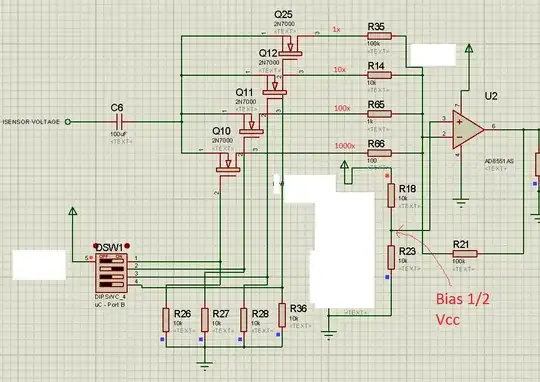

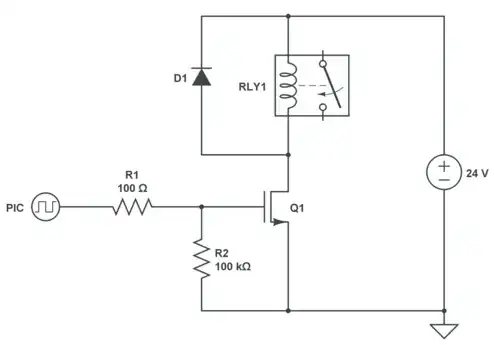

Why I'm that sure that no theoretical answer can be given unless we see the silicon schematic of this particular transistor? Well, the only hint Fairchild provided in the datasheet is that this transistor is of DMOS type. This could be helpfull in some way if the term DMOS was unambiguous, but it is not the case. There are many completely different topologies which called DMOS by different groups of engineers. Few examples:

These two references show at least three different topologies which may be reffered as DMOS, and there are more.

Anyone who is trying to explain how the transisto in question works without seeing the silicon implementation is just speculating (unless he works for Fairchild, in which case he discloses trade secrets :))