Quick answer: 90 deg bends are not an issue for most things. I don't do them purely from as aesthetic point of view. It only becomes an issue somewhere higher than about 500 MHz, but even then it's questionable.

There are three reasons to not do 90 deg bends: It causes an impedance mismatch, and thus messes up signal integrity. The sharp corners get rounded off during the PCB etching process and can weaken the trace. The bends cause some sort of reflection, unrelated to the impedance mismatch.

It has been shown that the impedance mismatch issue is a non-issue. There are many sources for this, but the best one is in the book "High Speed Digital Design: a handbook of black magic".

Weakening of the trace can be significant, particularly if your trace widths are on the edge of what the PCB shop can make. But I personally have never had issues with this, and don't know of anyone who has had an issue. So I can't say that it is a serious issue.

As for the wave of the signal bouncing off of the flat face of the trace, I am not sure if that is real or an EE urban legend. What I do know is that you need super fast edge rates to even bother thinking about this. Almost everyone here on EE.SE can ignore this.

What is more important than the shape of the trace is the "holy trinity of signal integrity": Trace Impedance, Signal Return Path, and Signal Termination. Get these right and almost everything else doesn't matter. Also, you should do this for almost all signals in a digital design, regardless of frequency!

Update: I'm adding stuff to directly address the schematic-like things the OP added to the question.

For starters, don't worry about the 90 deg thing. Not an issue.

Next, consider that SPI has two types of signals: One driver feeding one receiver, and one driver feeding multiple receivers. MISO and MOSI are examples of one driver feeding one receiver. SCLK, and CS are the signals the feed multiple receivers. Understanding this distinction is super important, since each type of signal will require different PCB layout techniques.

I'm going to describe how I deal with these signals. I rarely do 2 layer PCB's, most are 6 to 8 layers. What this means is that all of my PCB's have ground and power planes. This is super important, because properly handling signal integrity is almost impossible in a 2 layer board. Also, this is a big topic so I cannot write about everything. Where appropriate, I will give you terms to Google.

We'll start with the one driver feeding one receiver (MISO or MOSI), since this is the easiest. For these, I use a type of signal termination called "Source Serial Termination", or sometimes just called source termination. At the driver, in series with the signal, is a simple resistor of around 25 to 75 ohms. The exact value of this resistor has been calculated to match the impedance of the trace minus the source impedance of the driver. So if my trace is 50 ohms, and the driver has a 20 ohm output impedance then my resistor will be 30 ohms, +/- 10%.

The trace impedance can be calculated using the various formulas for "stripline" and "microstrip" traces (Google those). I normally target a 50 ohm trace impedance, and vary the trace width to get that. The signal layer of the PCB needs to be really close to the plane, otherwise the trace needs to be unrealistically wide. I construct my PCB Stackup (how the layers of the PCB are made up) to assure that the space between the signal layers and the plane layers is appropriate.

One reason why a 2-layer PCB is almost impossible to do this with is because the space between one layer and the next is super large and also you basically have no control over it. The other reason is that you rarely have a SOLID plane under your signal traces.

Another thing is that you rarely know the output impedance of your driver. Usually I just guess at about 10 ohms. Other times I'll just put a 50 ohm resistor there and expect to tweak the value once the PCB is made. I use a fast o-scope with proper ground connections and probing at the receiver when looking at the signal.

So, back to our signal... The resistor is placed as close to the driver as is reasonable. Then I route the signal directly to the receiver. Along the way I make sure the trace width is correct for the impedance I want. Next, I pay attention to the signal return path. Google "Signal Return Path" and "Loop Area". It is important that the signal return path say directly under the signal trace, and proper use of decoupling/bypass caps are used when the return path has to jump from the power plane to the ground plane or vice versa.

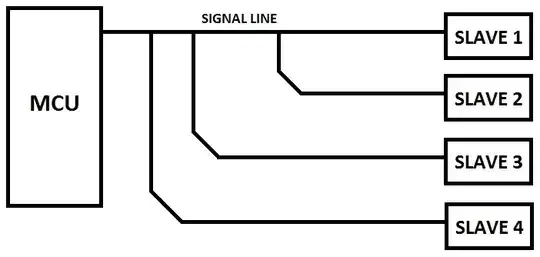

Now for the one driver-multiple receiver signals. These are much harder. The most important thing is that the signal must be daisy chained. In your case, the output of the MCU must go to slave 1, then from slave 1 to slave 2, then from slave 2 to slave 3. You cannot do it how you drew it in your diagram, where it goes out from the MCU and then branches out to all of the slaves. The second most important thing is that your signal termination must be at the very end of the line, after the last slave, and not at the MCU like the previous example.

(Note for the pedantic among us: What I said in the previous paragraph is not strictly true, *BUT... The single driver-single receiver has a difficulty of a 2 on a 1 to 10 scale. The daisy-chaining single driver-multiple receiver signal is about a 3 or 4. Doing a star routing, which is what you drew in your question, is about a 9 on our 1-10 scale. You can do it, but you'll regret it.)

For these signals, you have more options for your signal termination. The ideal termination would be a resistor from your signal to a power rail that is exactly half of your signal level. For example, if your signal goes from 0 to 3.3v then your resistor would go to a power rail that is 3.3/2, or 1.65 volts. The value of the resistor would equal the trace impedance (same microstrip/stripline formula as before). The regulator on this power rail needs to be a special type that is made for signal termination-- because it has to sink as well as source power (there are exceptions to this).

Of course, not everyone has a 1.65v rail just lying around, so there are options. If it's not a super critical signal, I might use a rail that is down to 1.5v, or as high as 1.8v. Or I might use two resistors, one to GND and one to +3.3v, instead of a single resistor (Google "signal termination" for the formulas). Or I might use a single resistor plus a cap in series, called AC termination.

The bad thing about using two resistors, like a voltage divider, as termination is that it can use up a lot of current. The good thing about AC termination is that it uses very little current. But many people get AC termination very wrong. AC termination only works for signals that have a 50% duty cycle and are always wiggling. Signals that do this are called clocks. :) But the SPI Clock does not apply, because it can be turned off and so it does not always wiggle. The other mistake that people make is that the cap is very small. Sometimes only a dozen pF. That cap should be at least 0.01 uF, and I often use 0.1 uF. A small cap here is a sure sign of someone not knowing what they are doing.

Anyway, so daisy chain these signals and put proper termination at the very end of the chain.

I have just barely scratched the surface of this issue, and it might take years before you fully understand the topic. There is a lot of info on the 'net about this, but unfortunately there is a huge amount of mis-information on the net as well. Beware.

I will end this with some things that should raise red flags. If you see any of this in some schematics, or in what someone writes, you need to run away: Just because the frequency of a clock, or the data rate, is slow does not mean it doesn't need signal termination. A 100 KHz digital signal usually requires proper signal integrity (SI) stuff just as much as a 100 MHz signal. Anytime someone add stuff to the circuit to "slow down the edges", that is a sure sign he/she doesn't have a clue. Anytime a cap is added directly to a signal, that's bad (with the exception of EMI filtering at connectors). As I mentioned before, using a pF-sized caps on AC termination. And finally, not verifying the SI with a good scope and proper probing can be fatal to your design.