In RS-232 specification, the stop bits can be 1, 1.5 or 2 stop bits...I wonder how it's possible to have half a bit?

Also some ADC math uses 0.5bit precision in the IC specifications/datasheet. Can someone elaborate in this subject?

In RS-232 specification, the stop bits can be 1, 1.5 or 2 stop bits...I wonder how it's possible to have half a bit?

Also some ADC math uses 0.5bit precision in the IC specifications/datasheet. Can someone elaborate in this subject?

In both of the cases you mention, an analog quantity is involved somewhere.

In the RS-232 case, the number of “stop bits” refers to a duration, so 1.5 stop bits simply means 1.5 times the duration of a bit at the given rate.

In the ADC case, 0.5bit precision refers to the analog quantity being converted, so 0.5bits essentially means that the digital result is guaranteed to represent the analog quantity rounded correctly to the nearest possible digital representation.

I wonder how it's possible to have half a bit?

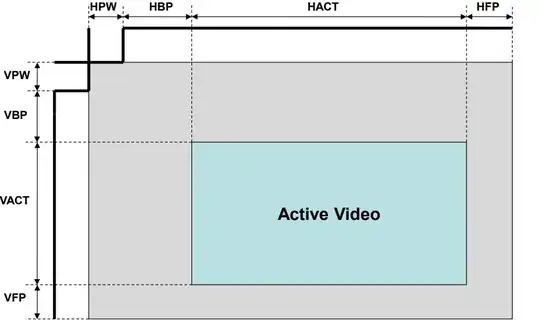

In UART based asynchronous serial communications (of which RS232 is an example), a serial byte of data is "enclosed" within a start bit and a stop bit(s). Following the stop bit there is a gap before the next data byte and this gap can be regarded as extending the stop bit(s): -

A lot of serial data transmission uses one stop bit because the receiver is able to process the bytes in the time but sometimes extending the gap between data bytes by increasing the number of stop bits is useful. As both sending and receiving UARTs have a much higher internal clock rate, manufacturing a fractional bit length is easy.

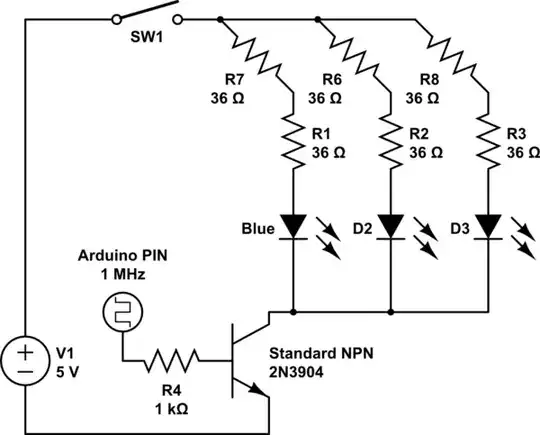

For an ADC, I've attached a drawing: -

The blue line represents a linearly rising analogue input voltage and the staircase is the digital number from the ADC trying to represent that analogue voltage. In the middle I've shown in red what the theoretical maximum error will be - no surprise it being equivalent to 0.5bits.