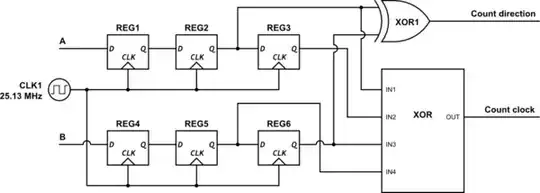

I am attempting to count pulses from a quadrature encoder in an Altera FPGA. I believe I have my counter set up correctly (circuit diagram below, following this tutorial), but when I turn my encoder on, the count just starts increasing non-stop. When I turn the encoder one way, the count speeds up, and when I turn it the other way it slows down, so it appears that I am in fact counting pulses, but also just counting up. Does anybody know why this might be?

simulate this circuit – Schematic created using CircuitLab

The count clock and count direction signals are going in to a 32-bit built-in counter function (LPM_COUNTER) on my Altera FPGA programmed using Quartus II v9.0. The output of this counter is stored in a buffer (LPM_BUSTRI) and read using a LabVIEW program whenever the LabVIEW code needs it. I have a similar LabVIEW code reading other buffers from the FPGA that is working fine, so I am fairly certain that the problem lies in my FPGA somewhere.

Your help is greatly appreciated!

EDIT: Corrected the displayed clock frequency.