I've been told that it's a bad idea to gate SCRs on when reverse-biased. Is that accurate? I'm reasonably confident that the SCRs won't actually conduct reverse-biased whether gated or not; are there circumstances where that is not true? Are there other problems with gating a reverse-biased SCR? Increased losses? Decreased lifetime?

-

Are we talking SCRs with or without (ASCR) reverse blocking. See http://en.wikipedia.org/wiki/Silicon-controlled_rectifier – JIm Dearden Jul 25 '13 at 17:43

-

Primarily with reverse blocking, though I'd be curious about any difference between them as well. – Stephen Collings Jul 25 '13 at 17:52

4 Answers

From an Infineon app note, page 19, 3.3.1.1.

Thyristors shall only be pulse triggered during the forward off-state phase. Positive trigger pulses during the reverse off-state phase will lead to significantly increased off-state losses due to the transistor effects caused. These losses adversely affect the functionality and may lead to destruction. Exception: For light triggered thyristors control pulses during the reverse off-state phase are permissible.

Infineon has told me that they can't really quantify the additional losses because it depends on reverse voltage, junction temperature, part number, and the exact unit you happen to have.

I also received this from SanRex today:

When the SCR is reverse biased and a gate signal is present, reverse leakage current will go up typically by 10 times or more. This increased reverse current will cause over temperature on certain areas of the die, which will deteriorate the die itself.

- 17,373

- 17

- 92

- 180

In a former life where I worked in power electronics we would not gate the SCRs on in reverse conduction because it reduced the reverse blocking capability of the SCR. It would therefore be easier for an inductive spike or other transient to force the SCR on and ultimately lead to its destruction.

I don't have any evidence to back this up, it was "tribal knowledge" from our greybeard engineers. We were also working on medium voltage (up to 4kV) and high voltage (13kV and up) systems where we had a number of SCRs in series and it was very important to maintain reverse blocking voltage.

- 11,162

- 1

- 35

- 62

I have had considerable experience with triggering anti-parallel SCRs used as AC switches on mostly inductive loads. This was for circuit breaker test sets that used 480 VAC primary transformers with secondaries of typically 6 to 18 volts, and producing short term (several cycles) current up to 100,000 amps. We found that we had the best results by driving both gates with DC, initially at a phase angle of 60 to 90 degrees, and maintaining the drive until turning it off. Since both SCRS are ON, reverse blocking is not an issue.

Applying voltage at an initial phase angle of up to 90 degrees, into an inductive load, serves to eliminate a phenomenon known as DC offset, where a zero-crossing trigger will produce a current peak up to twice that at which it eventually stabilizes.

- 7,195

- 1

- 7

- 23

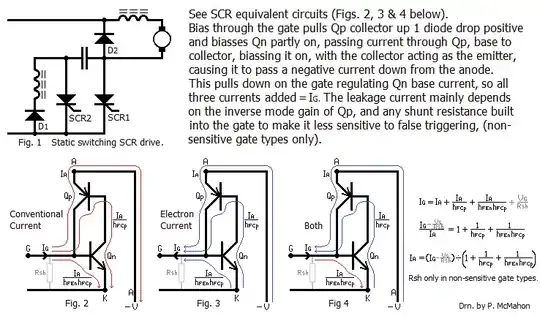

I was testing a static switching SCR drive like the one in Fig. 1, for a battery operated coil transporting machine, but it had an SCR instead of D1, so I biased it on to make it act as a diode, and found it was discharging the capacitor instead of blocking the current after the inductor reversed it's charge, so I connected a diode between it's gate and anode to trigger it when forward biased.

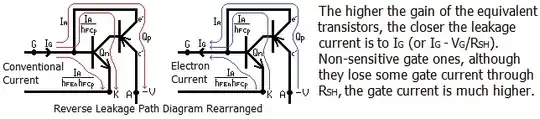

Later, I worked out how the reverse leakage occurred. See diagram below.[

- 381

- 1

- 7