Can anyone tell me the difference between If-Else construct and Case statement constructs of a process in VHDL in terms of how the code is inferenced into RTL circuit by the synthesis tool ?

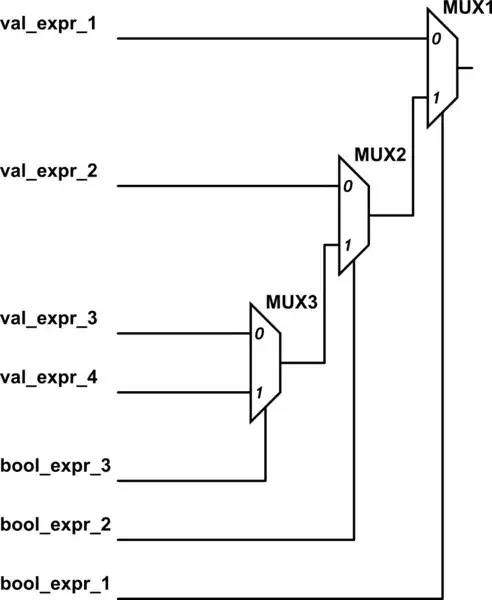

The if-elsif-else construct infers a priority routing network:

simulate this circuit – Schematic created using CircuitLab

This corresponds to

if bool_expr_1 then

sig <= val_expr_1;

elsif bool_expr_2 then

sig <= val_expr_2;

elsif bool_expr_3 then

sig <= val_expr_3;

else

sig <= val_expr_4;

end if;

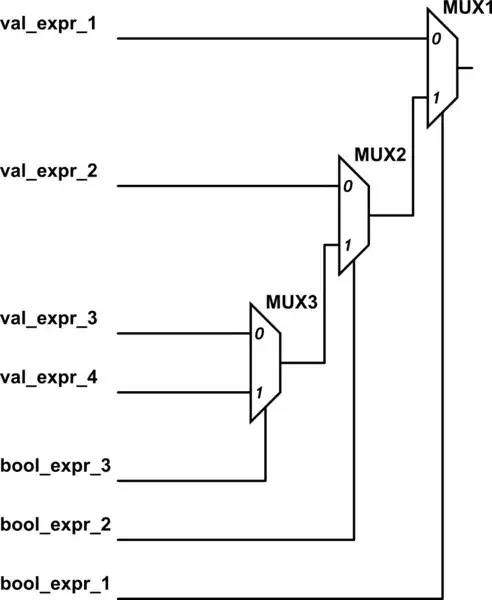

The case construct, on the other hand, infers a big ol' mux:

This corresponds to

case case_expr is

when c0 =>

sig <= val_expr_0;

when c1 =>

sig <= val_expr_1;

when c2 =>

sig <= val_expr_2;

...

when others =>

sig <= val_expr_N;

end case;

Obviously these are very simplified designs with only one value expression, resulting in one output.

Do consider the case of multiple nested if-else and mixing case-statements with if-else construct inside a process.

Per the above, you can see how they would nest/mix.

Also when to use which construct ?

Since if-else infers priority, it should be used when more than one input condition could occur. Using case, one the other hand, is appropriate when the inputs are mutually exclusive.