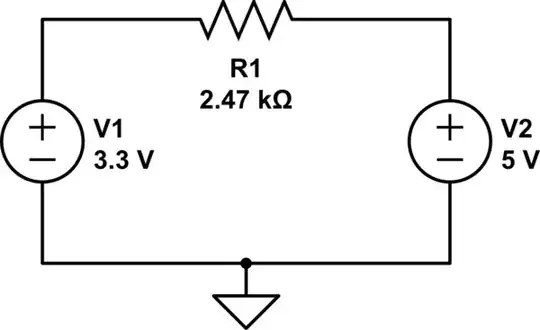

Let's assume the following scenario:

- uC (@3.3V VDD) drives an I/O pin HIGH 3.3V (just to be clear, it's not an open-drain pin, so the p-channel mosfet of the output pin is actually driving the pin to VDD level)

- Pin is also rated as a 5V tolerant input (so it's not clamped to VDD).

- The line that the pin is driving is also connected to a pin of another uC(@5V VDD) which may drive the line to 5V level also

- Between the two pins of the different uC's we assume an ~2470R resistance

The questions are:

What happens if while the 3.3V uC drives the line HIGH (3.3V), the other uC also tries to drive the line HIGH (5V)? What can then be stated about the 5V tolerance of the 3.3VDD uC OUTPUT pin?

Is then a 680uA current ( (5 - 3.3) / 2470 ) sinked to the VDD of the 1st uC? What does actually happen inside the I/O pin circuitry of the 1st uC? Is this inter-connection safe?

I post this question in case someone with a better understanding of is cares to answer, as this case is not documented in the uC datasheet and I couldn't find any definitive reference on this after doing a fair bit of research.