For a few small 2 layers boards I'm doing, I'm using the top layer for parts and signals and a ground pour on the bottom layer with no or very short traces, based on comments and answers to my previous question

Since the top layer becomes too chopped-up with a lot of islands, which makes it practically useless and I'm also trying to minimize the current loop between the ICs and decoupling caps (if I leave the top layer it will connect to the caps and the ground pins separately and not in a single point), so I decided not to use a copper pour on the top layer at all for the mentioned reasons.

The problem with this approach is the manufacturing side of things, if I understand correctly FR4 material could wrap if the copper on both sides of the PCB is unequal (although I don't understand why that doesn't happen with a 4 layer board typical stack-up sig-gnd-vcc-sig), so I'm back where I started

I've been going back to this a lot doing a lot of research but still can't find a conclusive answer and I can't decide what to do.

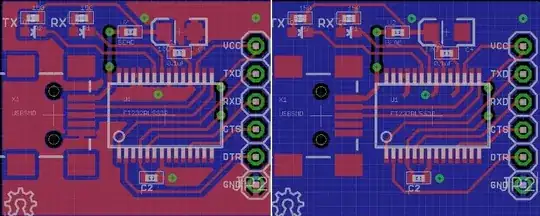

This is an example board, the one on the right without top copper pour.

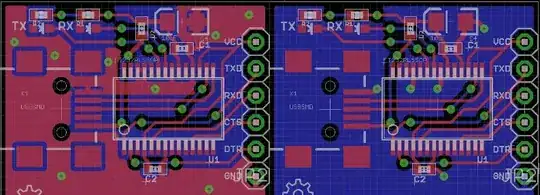

Update: based on your comments, I revised the board to avoid breaking the ground as much as possible, but still can't decide on the top layer though.

Update: based on your comments, I revised the board to avoid breaking the ground as much as possible, but still can't decide on the top layer though.