I have a board with an Altera EPF10K30RC240-4N that is not functioning at all. There is a high current draw on the board. The +5V rail is only 2.6V and there is 4.2 ohms between +5V and GND.

The board is a plug-in module for a larger assembly. It has been operating without fault for over 20 years, so no, the chip is not installed incorrectly. When a known good board is installed, the system works perfectly; it is not the power supply. Nor is it the clock or the program, that would not explain the 4.2 ohms to ground.

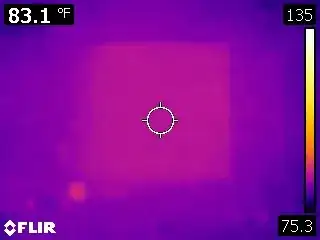

Looking at the board with a thermal camera, the FPGA is the only device that is heating up abnormally. The entire chip gets warm within seconds. Comparing the thermal image to the working board, it should only be a few degrees above ambient temperature when running.

The question is: what would cause an entire FPGA package to heat up evenly across the whole device? If there was a shorted gate or I/O driver, I would expect to see a heat bloom at that specific spot on the die.

FPGA heating up over 52 seconds (low-res 320x240 camera):

ADDENDUM 08/31/23

I removed the chip and discovered a blow-out on the bottom side. After removal, the resistance between the +5V and GND rails on the board went to 3.9k. So the chip is shorted internally and is dead, as was mentioned in the two answers below. (Excuse the bent pins, I clumsily dropped the chip immediately upon removal {roll eyes}).