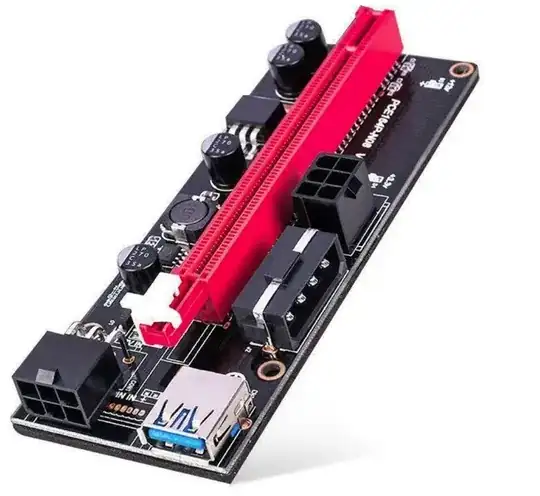

Is PCIe normal USB 3.0? So, can I use a PCIe interface of a PC as a normal USB 3.0?

In this particular case, no. As others have explained, USB 3.0 cables are only used as convenient high-speed transmission lines for PCIe signals, since USB cables are one of the most common and cheapest cables suitable for high-speed signaling in existence due to USB's popularity in customer electronics.

However, there are indeed a lot of commonalities between the physical layers of USB 3.0 and PCIe.

In USB 2.0 high-speed signaling (480 Mbps), a custom non-standard design was adopted. Electrically it uses LVDS-like signaling, but it's not really compatible with any other LVDS transceivers. Rather than using a pure differential design, it contains both single-ended and differential signals. The signaling is half-duplex over only a single differential pair, further complicating the transceiver design due to the need of bus arbitration. As a result, transparent USB repeaters, common-mode filters, and galvanic isolators are difficult to implement in USB 2.0.

After these problems were recognized, USB 3.0 signaling took a standardized approach better aligned with industry practices. It features:

- Full-duplex RX and TX over two pairs of unidirectional differential pairs.

- AC coupled, 8b/10b encoding for DC balancing.

- Current-Mode Logic.

This type of signal is commonly found in almost all high-speed digital systems, including USB 3 and PCIe, many standard hardware interfaces and transceivers exist. Thus, for the sake of following the de-facto industrial standards, USB 3.0's physical layer is largely based on PCIe. For example, the text on 8b/10b encoding in the USB 3.0's specification is identical to PCIe's down to the wordings. Some concepts in the protocol even have the same name - the Link Training and Status State Machine exists in both PCIe and USB 3.

The use of standard high-speed signaling schemes by USB 3 allows ASIC designers to reuse the PCIe transceiver circuitry in some case. For example, Intel's PIPE (The PHY Interface for the PCI Express) architecture is a transceiver capable of transmitting PCIe, USB 3, SATA and DisplayPort at the same time.

In fact, USB 3 signals are "standard" enough that you can transmit it over fiber optics by running the differential pair directly into an unmodified SFP+ 10 Gigabit Ethernet transceiver, due to the fact that SFP+ transceivers are protocol-agnostic electrical-to-optical converters that accept an arbitrary CML signal. Without doing anything else, the result you'd get is 80% functional (proper power management is a challenge).

On the other hand, there are some important differences.

To be backward-compatible, all USB 3 devices are required to have a separate USB 2 transceiver, which hasn't changed. Thus, all USB 3 hosts, hubs, devices and ports are in fact two ports: a USB 2 port and a USB 3 port glued together, running on separate data lines. When operating in USB 2 mode, the device cannot benefit from USB 3's improvements. None of the described similarities apply to USB 2.0, or a USB 3 device in USB 2 mode.

USB 3 and PCIe use different protocols above the physical layer, the controller and software involved are entirely different. It's not possible to speak USB over PCIe, unless you've implemented a real USB 3 controller (Or unless we're talking about USB 4, with Thunderbolt-like PCIe tunneling support).

USB 3 uses Low-Frequency Periodic Signaling (LFPS) for link establishment and power management. This is a custom out-of-band signaling system that doesn't exist in PCIe and many other high-speed protocols.

USB 3.1, USB 3.2, and USB 4 introduced many extensions, including multi-lane operation in USB 3.2 Gen 2x2, so its similarity to PCIe at the physical layer is not as similar as it was in the USB 3.0 days.