They are very relevant!

So first off: bonding wires have very little surface, so the capacitance between them is low; they are also relatively short, so that their mutual inductance is low.

But: at higher frequencies they become a problem. (Also because they represent a break in characteristic impedance; that's one of the reasons why you often see packages that don't depend on bond wire, such as chip-scale flip-chip packages, for very high speed applications.)

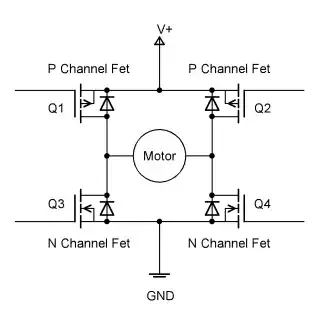

On the chip level, the fact that there's significant capacitance between nearby elements is the very basic principle on which many (actually, probably most) semiconductor chips work: the field-effect transistor (FET) only works exactly because a gate together with the drain-source junction form a capacitor.

This of course means that when designing a chip, you need to make it so that capacitive coupling only happens where you want it, and that is an important design constraint already "baked" into how the layer stackup is constructed; you still must not put e.g. large metal areas close to each other, unless you want to construct a capacitor.

In the end, everything has stray capacitance to everything – that's just how the universe is. Your job as an engineer is to suppress all the stray effects such that the effects you want become dominant and the whole system manageable. There's simple examples of that: your bicycle wheels don't have to be perfectly round (such a thing does not exist), they just need to be round enough so that pedalling makes you move significantly more forward than sideways and up and down. That's the case here, as well: all the (potentially billions!) of parts in a semiconductor device need only be isolated from each other well enough that the intended currents are large enough compared to the unintended ones so that, even under thermal noise, the device still works reliably.

Of course, that means that if you need to design a high-performance chip, you'll work close to these reliability limits – for example, you make gate capacitances as small as possible (to reduce the time it takes to switch a MOSFET by charging or discharging the gate). But of course, that means that smaller stray capacitances could start to significantly change the state of the MOSFET, if a high-frequency current was applied across them.

That is exactly what the so-called Rowhammer vulnerability in modern computer memory is based on: A module of computer memory (RAM) consists of billions of MOSFETs, whose gate charge defines whether they're set to a logical "1" or a "0". Not only speed, but also size, require that these MOSFETs have very small gates and are very tightly and regularly packed. As fantastically reliable as modern RAM is, if you write software that just toggles the same bits very rapidly, you might find that surrounding MOSFET gates get charged as well, due to crosstalk between different MOSFETs and their connections.