I am working with an IGLOO2 device and attempting to instantiate a RAM1K18 IP into my design using the SmartDesign Tool in Libero 2023.1. I have a basic testbench in which I establish an address, and attempt to write to it, and read back the data. However, in sim I see both "A_DOUT" and "B_DOUT" all 0's. The "Busy" signal is constant 'z'

I have tried extending my sim to 1ms, which I feel is plenty of time, however the signals remain. I have ported a design onto HW with the same IP using a similar method of writing / reading and am seeing 0's for my DOUT signals there as well though there I see constant '0' instead of constant 'z'.

Testbench snippet:

--Generate the test stimulus

tb1 : process

begin

--Pre reset

wait for CLK_PERIOD*10;

--Toggle reset

wait for CLK_PERIOD*5;

RESET_N <= '0';

wait for CLK_PERIOD;

RESET_N <= '1';

wait for CLK_PERIOD*10;

-- First write to testRAM

wait for CLK_PERIOD*100;

A_ADDR <= "00000010000000";

B_ADDR <= "00000011000000";

A_DIN <= "000000000010000000";

B_DIN <= "000000000011000000";

A_WEN <= "11";

B_WEN <= "11";

wait for CLK_PERIOD;

--Change from wr to rd

A_WEN <= "00";

B_WEN <= "00";

wait for 100 us; --maybe wait a long time?

-- Second write to testRAM

A_ADDR <= "00000100000000";

B_ADDR <= "00000100000000";

A_DIN <= "000000000100000000";

B_DIN <= "000000000100000000";

A_WEN <= "11";

B_WEN <= "11";

wait for CLK_PERIOD;

-- Change from wr to rd

A_WEN <= "00";

B_WEN <= "00";

wait for 100 us; --maybe wait a long time?

--Rd from first address set

A_ADDR <= "00000010000000";

B_ADDR <= "00000011000000";

wait for 100 us; --maybe wait a long time?

Generated Entity from SmartDesign:

----------------------------------------------------------------------

-- Created by SmartDesign Wed Jul 19 12:24:41 2023

-- Version: 2023.1 2023.1.0.6

----------------------------------------------------------------------

----------------------------------------------------------------------

-- Libraries

----------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

library smartfusion2;

use smartfusion2.all;

----------------------------------------------------------------------

-- sd_ram1k18 entity declaration

----------------------------------------------------------------------

entity sd_ram1k18 is

-- Port list

port(

-- Inputs

A_ADDR : in std_logic_vector(13 downto 0);

A_ARST_N : in std_logic;

A_BLK : in std_logic_vector(2 downto 0);

A_CLK : in std_logic;

A_DIN : in std_logic_vector(17 downto 0);

A_DOUT_ARST_N : in std_logic;

A_DOUT_CLK : in std_logic;

A_DOUT_EN : in std_logic;

A_DOUT_LAT : in std_logic;

A_DOUT_SRST_N : in std_logic;

A_EN : in std_logic;

A_WEN : in std_logic_vector(1 downto 0);

A_WIDTH : in std_logic_vector(2 downto 0);

A_WMODE : in std_logic;

B_ADDR : in std_logic_vector(13 downto 0);

B_ARST_N : in std_logic;

B_BLK : in std_logic_vector(2 downto 0);

B_CLK : in std_logic;

B_DIN : in std_logic_vector(17 downto 0);

B_DOUT_ARST_N : in std_logic;

B_DOUT_CLK : in std_logic;

B_DOUT_EN : in std_logic;

B_DOUT_LAT : in std_logic;

B_DOUT_SRST_N : in std_logic;

B_EN : in std_logic;

B_WEN : in std_logic_vector(1 downto 0);

B_WIDTH : in std_logic_vector(2 downto 0);

B_WMODE : in std_logic;

SII_LOCK : in std_logic;

-- Outputs

A_DOUT : out std_logic_vector(17 downto 0);

BUSY : out std_logic;

B_DOUT : out std_logic_vector(17 downto 0)

);

end sd_ram1k18;

----------------------------------------------------------------------

-- sd_ram1k18 architecture body

----------------------------------------------------------------------

architecture RTL of sd_ram1k18 is

----------------------------------------------------------------------

-- Component declarations

----------------------------------------------------------------------

-- RAM1K18

component RAM1K18

generic(

MEMORYFILE : string := "" ;

RAMINDEX : string := ""

);

-- Port list

port(

-- Inputs

A_ADDR : in std_logic_vector(13 downto 0);

A_ARST_N : in std_logic;

A_BLK : in std_logic_vector(2 downto 0);

A_CLK : in std_logic;

A_DIN : in std_logic_vector(17 downto 0);

A_DOUT_ARST_N : in std_logic;

A_DOUT_CLK : in std_logic;

A_DOUT_EN : in std_logic;

A_DOUT_LAT : in std_logic;

A_DOUT_SRST_N : in std_logic;

A_EN : in std_logic;

A_WEN : in std_logic_vector(1 downto 0);

A_WIDTH : in std_logic_vector(2 downto 0);

A_WMODE : in std_logic;

B_ADDR : in std_logic_vector(13 downto 0);

B_ARST_N : in std_logic;

B_BLK : in std_logic_vector(2 downto 0);

B_CLK : in std_logic;

B_DIN : in std_logic_vector(17 downto 0);

B_DOUT_ARST_N : in std_logic;

B_DOUT_CLK : in std_logic;

B_DOUT_EN : in std_logic;

B_DOUT_LAT : in std_logic;

B_DOUT_SRST_N : in std_logic;

B_EN : in std_logic;

B_WEN : in std_logic_vector(1 downto 0);

B_WIDTH : in std_logic_vector(2 downto 0);

B_WMODE : in std_logic;

SII_LOCK : in std_logic;

-- Outputs

A_DOUT : out std_logic_vector(17 downto 0);

BUSY : out std_logic;

B_DOUT : out std_logic_vector(17 downto 0)

);

end component;

----------------------------------------------------------------------

-- Signal declarations

----------------------------------------------------------------------

signal A_DOUT_net_0 : std_logic_vector(17 downto 0);

signal B_DOUT_net_0 : std_logic_vector(17 downto 0);

signal BUSY_net_0 : std_logic;

signal A_DOUT_net_1 : std_logic_vector(17 downto 0);

signal B_DOUT_net_1 : std_logic_vector(17 downto 0);

signal BUSY_net_1 : std_logic;

begin

----------------------------------------------------------------------

-- Top level output port assignments

----------------------------------------------------------------------

A_DOUT_net_1 <= A_DOUT_net_0;

A_DOUT(17 downto 0) <= A_DOUT_net_1;

B_DOUT_net_1 <= B_DOUT_net_0;

B_DOUT(17 downto 0) <= B_DOUT_net_1;

BUSY_net_1 <= BUSY_net_0;

BUSY <= BUSY_net_1;

----------------------------------------------------------------------

-- Component instances

----------------------------------------------------------------------

-- RAM1K18_0

RAM1K18_0 : RAM1K18

port map(

-- Inputs

A_CLK => A_CLK,

A_DOUT_CLK => A_DOUT_CLK,

A_ARST_N => A_ARST_N,

A_DOUT_EN => A_DOUT_EN,

A_BLK => A_BLK,

A_DOUT_ARST_N => A_DOUT_ARST_N,

A_DOUT_SRST_N => A_DOUT_SRST_N,

A_DIN => A_DIN,

A_ADDR => A_ADDR,

A_WEN => A_WEN,

B_CLK => B_CLK,

B_DOUT_CLK => B_DOUT_CLK,

B_ARST_N => B_ARST_N,

B_DOUT_EN => B_DOUT_EN,

B_BLK => B_BLK,

B_DOUT_ARST_N => B_DOUT_ARST_N,

B_DOUT_SRST_N => B_DOUT_SRST_N,

B_DIN => B_DIN,

B_ADDR => B_ADDR,

B_WEN => B_WEN,

A_EN => A_EN,

A_DOUT_LAT => A_DOUT_LAT,

A_WIDTH => A_WIDTH,

A_WMODE => A_WMODE,

B_EN => B_EN,

B_DOUT_LAT => B_DOUT_LAT,

B_WIDTH => B_WIDTH,

B_WMODE => B_WMODE,

SII_LOCK => SII_LOCK,

-- Outputs

A_DOUT => A_DOUT_net_0,

B_DOUT => B_DOUT_net_0,

BUSY => BUSY_net_0

);

end RTL;

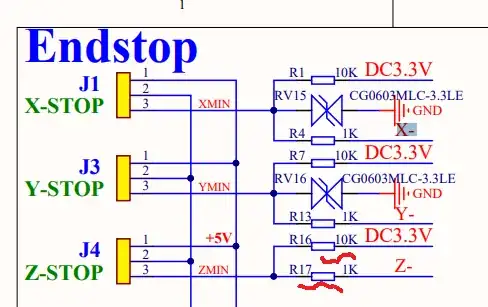

Zoomed in waveform (initial values & and setting A_WEN to "11" (write en)):

Zoomed out waveform showing no change in busy signal:

I have been using this doc (pages 54 - 61) for reference: https://www.microsemi.com/document-portal/doc_view/130906-smartfusion2-and-igloo2-macro-library-guide

I look forward to your responses and appreciate the help.