As @Seth answer indicates, plated via-in-pad is the technology used to acheive this. For really dense chips this is frequently in combination with laser drilled blind micro-vias, though that is beyond most PCB pooling companies.

In your case as there are not many balls to pin out a simple plated via in pad to get to other layers should make things possible. As mentioned JLC support this POFV option if requested on 4L (or by standard on >6L).

Indeed looking at the pinout for the chip, most of the balls are "NC" which the datasheet indicates are not electrically connected to anything. This means you can route e.g. power traces through those other balls to help escape route things. When doing this, leave the pads on the PCB so the balls get connected otherwise assembly may fail, but you can assign the NC pads to whatever purpose you wish to help you escape route.

Regarding JLC, make sure you read their guidelines if you plan to do via in pad. Specifically they say for BGA via-in-pad with POFV:

The vias are filled with either conductive or non-conductive epoxy. Minimum drill is 0.2 mm, so use >=0.3 mm pads.

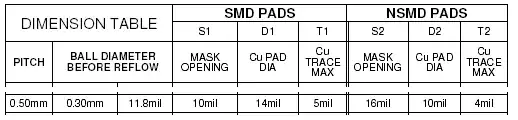

Because of this restriction, the pad size for your BGA must be set to at least 0.3mm, with a 0.2mm drill to use the via-in-pad option here. This is quite large for a 0.5mm pitch BGA, but not insurmountable.

When choosing the size of the BGA pad, you should consult with either the manufacturers recommended sizes, or if not specified, make use of tables listing common pitch/ball sizes to determine the specific required solder mask openning and pad sizes.

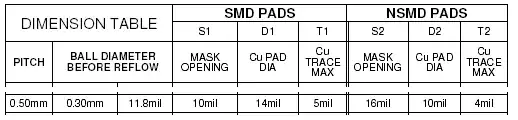

Your device datasheet indicates a pitch of 0.5mm and a ball diameter of nominally 0.3mm. Based on the tables here, you will have to go for the "Solder Mask Defined (SMD) Pad" approach. For this pitch/ball diameter, the table calls out:

Note that for the NSMD option, the copper pad size required 0.26mm (10 thou) which is too small for the JLC via, and therefore cannot be used.

Instead, for the SMD option, the table gives a copper pad size of 0.35mm (14 thou). This is larger than the size of the via annulus so should work well. Then make the aperture in the solder mask of 0.26mm (10 thou).