I'm working with audio codecs, and I have to put a lot of them (32) on a PCB.

The fact that I have to connect so many ICs makes the board pretty big with very long tracks. I've read a lot about how to handle the design properly to avoid crosstalk and interferences, but I'm still struggling to find a definitive answer.

So, I want to connect 32 MAX98357 codecs in TDM (Time-division multiplexing) mode. This codec also acts as a small amplifier. I control them with a FPGA Zynq (Zybo Z7). The FPGA controls only 3 digital signals per codec (Bit Clock, Word Select, and Data). They all share the same two clocks (Bit Clock and Word Select), which are around 100MHz. Each bank of 8 codecs shares the same Data line (the codecs know his slot thanks to a resistor).

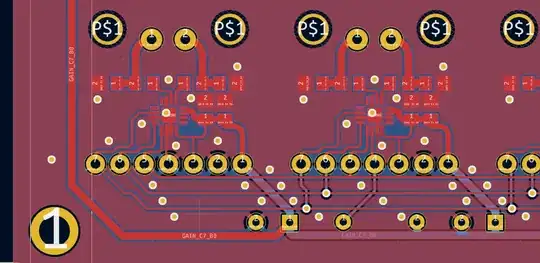

To achieve this, I basically replicated the layout from the Adafruit breakout board 32 times. Additionally, I added a clock buffer (551SDCGI) for the 3 digital signals and put 8 codecs per output.

Below is one bank of 8 codecs and their connections: (I highlighted a clock line)

The signal comes from the right connector, goes through the clock buffer, and is then distributed to all of the codecs.

The big capacitor in front of each of them is to stabilize the power supply because they are all amplifiers too, but I'm not entirely sure about this part.

Due to PCB constraints, I can only use a 2-layer PCB. I poured GND on each side and added stitching vias as shown below:

The 3 parallel lines are my 3 digital signals (clock and data).

Now, my question is about the stitching vias. Is my implementation okay, or is it overkill?

From what I read, since the maximum frequency is 100MHz, even if I take 1/20 of the wavelength as the distance between vias, it might be overkill (3m/20=15cm).

On the other hand, I also read that if I just pour GND between lines without stitching it, I will have an antenna effect.

So, what should I do? Is it enough to have GND on the bottom layers without top and stitching vias?

Do I have to calculate the wavelength with 100MHz, or is it different because it's a square digital signal?

I know this question is pretty frequent, but I never find this kind of strange implementation (not to high frequency but very long track) I hope I give enough information for you to help me...