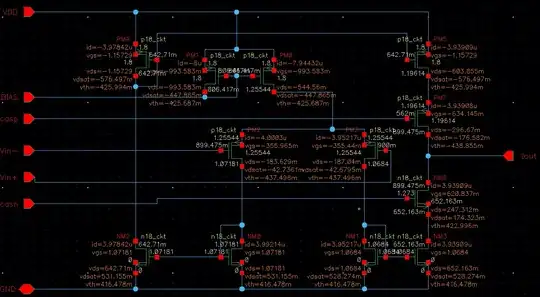

I am trying to determine the sizing of transistors in the OTA as shown below. A strange thing I found earlier was that a small output impedance of M5 would cause a much smaller GBW than designed, as explained by sai in a previous question.

However, as I increase the widths of M7 and M8 (from 6uM to 9uM), while keep their lengths unchanged (19uM), the UGB decreases again (from 713k to 706k). My initial guess was that the output impedance of M7 decreased (from 25M to 21M), so some of the signal current failed to pass through M7 to M8, causing the overall transconductance decreased.

The problem is that increasing the widths of M3-M6 increases the UGB (can be 730k if the widths are set 9uM), which contradicts the "current wasted on small output impedance" theory, as the output impedance of M3-M6 also decreases when their widths increase.

My question is: What affects the UGB in this case? Why does increasing the width of the NMOS and PMOS produce opposite results?

I also attached the DC simulation result below, for W7 and W8 = 6uM,