The TDK NLV32T-221J-PF is a ferrite core 220 uH inductor with a 50 mA rated current. The inductor will probably saturate before the current limit mechanism of the 34063 turns the switching transistor off. When the core saturates, current will rise very quickly. If the current rises quickly enough, and the 34063 is not quick enough in responding and shutting off the switching transistor, there could be excessive currents for a brief time. These excessive currents could be responsible for the overheating of the 34063. The core saturation could be responsible for the low output voltage.

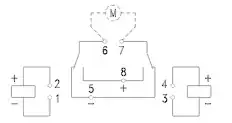

Choose an inductor that is sufficiently rated for the maximum current of the 34063 is expected to handle. With a 0.22 \$\Omega\$ resistor between Vcc and Vpksense (pins 6 and 7) Ipk will be 0.3/0.22 = 1.36A.

Alternatively, choose a sense resistor that is sufficiently large that the current will be limited before the inductor reaches its rated current.

To be honest, I never really understood what the SENSE does in the datasheet so i left it like that..... Could you please explain its function?

Briefly, the 34063 has a timing capacitor that determines the maximum \$t_{on}\$ for the switching element (i.e. \$t_{on(max)}\$) and the minimum \$t_{off}\$ for the switching element (i.e. \$t_{off(min)}\$. Note that the inductor may stop conducting before the \$t_{off}\$ period is complete. If the feedback voltage \$V_{fb}\$ is above 1.25 V, the actual \$t_{off}\$ will be greater than \$t_{off(min)}\$. If the instantaneous voltage between the \$V_{cc}\$ pin and the \$I_{pk(sense)}\$ pin is above about 0.3V, then the actual \$t_{on}\$ will be less than \$t_{on(max)}\$. Thus, these three parameters, the capacitance of the timing capacitor, \$V_{fb}\$, and the potential difference between the \$V_{cc}\$ pin and the \$I_{pk(sense)}\$ pin together regulate the duty cycle and frequency of the converter as well as the peak current through the switch.

Further details: The 34063 generates a triangular current wave through the inductor in the following manner:

A timing cycle begins when the voltage on the timing capacitor is less than or equal to 0.75V. When the cycle starts, the chip begins charging the timing capacitor. If \$V_{fb} \le 1.25V\$ during the charging of the timing capacitor, the 34063 turns the switching transistor on. A rising current begins to flow through the switch, the inductor, and the sense resistor. The rising current through the sense resistor causes a rising voltage across it. The \$t_{on}\$ phase of a cycle ends when either the voltage across the timing capacitor reaches 1.25 V, or when the potential difference between the \$V_{cc}\$ pin and the \$I_{pk(sense)}\$ pin reaches approximately 0.3 V. Thus, the timing capacitor determines the maximum \$t_{on}\$ for the switching element, but if the \$I_{pk(sense)}\$ pin reached the voltage \$V_{cc} - 0.3 V\$, or if \$V_{fb} \ge 1.25V\$ at the start of the \$C_T\$ charging phase of a cycle, then the actual \$t_{on}\$ will be less than \$t_{on(max)}\$. It is possible, due to \$V_{fb}\$, that the switch does not turn on at all during a timing capacitor cycle.

If the potential difference between the \$V_{cc}\$ pin and the \$I_{pk(sense)}\$ pin reaches 0.3 V before the voltage of \$C_T\$ reaches 1.25V, then the timing capacitor is quickly charged to 1.25V. In either case, the switching transistor is turned off at this at the end of the timing capacitor charging phase.

At this point, the chip starts to discharge the timing capacitor. With the switching transistor off, the current through the inductor begins to fall. When the timing capacitor discharges to 0.75 V, the chip will stop discharging the timing capacitor, and begin a new timing capacitor charging phase. Thus, the timing capacitor also determines the minimum value of \$t_{off}\$, but if \$V_{fb} \gt 1.25 V\$, the actual value of \$t_{off}\$ will be greater than \$t_{off(min)}\$.

[Note that the 34063 uses different levels of current to charge and discharge the timing capacitor. Thus, \$t_{on(max)} \ne t_{off(min)}\$, but rather \$t_{on(max)} \approx 6 t_{off(min)}\$]

The \$I_{pk(sense)}\$ pin controls the peak current through the switch. This is useful in limiting the peak current through the inductor so that it does not saturate. However, the relationship between the feedback provided by \$I_{pk(sense)}\$ and the average output current (or the average current through the switching transistor or the average current through the inductor) is not so straightforward, and depends upon whether the converter is operating in Continuous Conduction Mode (CCM) or Discontinuous Conduction Mode (DCM), among other things such as the topology of the converter. For that reason, I will not go into detail about the relationship between peak switching current, and average output current. Suffice it to say that they are sufficiently different to require separate analysis.

[A converter is said to be in DCM if the inductor current reaches 0 before the end of the \$t_{off}\$ phase. If there is still residual current flowing in the inductor at the end of the \$t_{off}\$ phase, then the converter is said to be operating in CCM.]