You're very close. The simulation in CircuitLab does not account for the schmitt trigger inputs of the CD4093, and so you won't see the true duration of output pulses. Also, the gates are not simulated with any particular supply voltage, so their outputs are "digital high or low", showing up as 1 or 0 on the graphs. If you want to simulate this properly, use LTSpice, or something similarly high-tier.

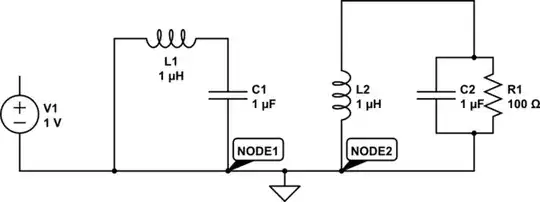

The circuit I suggest is as follows:

simulate this circuit – Schematic created using CircuitLab

This employs a single-throw "open/closed" switch, instead of your double-throw relay switch, since that's how you described it in the question. R3, R4 and C3 debounce the switch contacts, and I also added gate G3 to clean up and buffer the switch signal. The schmitt trigger inputs of the CD4093 will help enormously with immunity to noise and interference. You probably couldn't get away with such large values for R3 and R4 if using regular gates, so don't use regular gates.

The only real long-term current drain from the power supply is due to R3 and R4. When the switch is closed, these resistors cause about 10μA to flow from the supply. You could increase those resistances to decrease current, but I feel that they are already very high. I don't see any simple alternative, if you use a single-throw switch.

G3 also adds symmetry to charging and discharging of C1 and C2. Both paths now have similar source impedance driving them (and other characteristics), to keep the two pulses of similar duration.

When using schmitt trigger input gates, the switching thresholds will be near \$\frac{1}{3}\$ and \$\frac{2}{3}\$ of the supply, which means that the duration of the pulses will be very close to time constants \$R_1C_1\$ and \$C_2R_2\$. The values I use of 10μF and 470kΩ should yield pulse durations close to 4 or 5s.