In general, all real implementations of electronic logic gates have an input current. Some very low, some quite high, some like a resistive load, some like a capacitive load, and anything in between or outside. There are many different techniques, old ones like DTL or TTL and newer ones like CMOS.

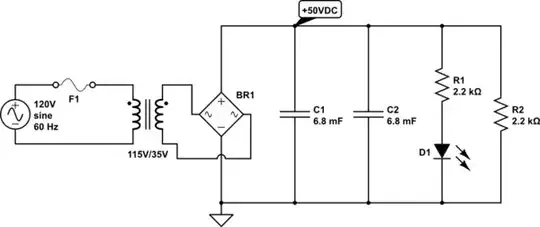

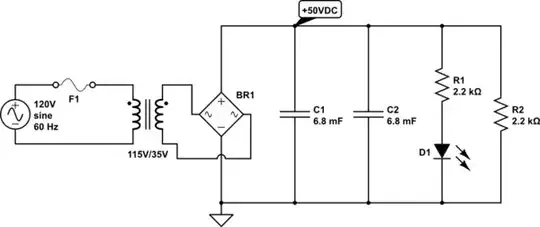

The linked example shows this schematic:

simulate this circuit – Schematic created using CircuitLab

These resistors are used to provide the respective logic level, if the SPST switch is open. You cannot replace it with a direct wire, as it will short the source of the logic level, commonly ground or supply voltage, with the other side, when the switch is closed. Such a resistor limits the current when the switch is closed.

Anyway, your question is useful. What about the voltage drop because of the input current?

As we now know, there are different techniques. You need to know the input current to design the resistor in a way that the input accepts the voltage as the desired logic level. Techniques with a very low input current get away with bigger resistors, others with a very high input current need smaller resistors.

For example, a standard TTL low-power-Schottky input has these parameters:

\$V_{CC} = 4.75 V\$ (minimum)

\$V_{IH} = 2 V\$ (minimum)

\$V_{IL} = 0.8 V\$ (maximum)

\$I_{IH} = 20 µA\$ (maximum)

\$I_{IL} = -0.4 mA\$ (maximum)

Note: the negative sign on \$I_{IL}\$ designates that current as "sourcing" from the input.

For a working pull-down, the resistor needs to generate a voltage drop of maximum 0.8 V for the maximum input current of 0.4 mA. So it has to be less than or equal to:

\$R_{PDmax} = \frac{V_{max}}{I_{max}} = \frac{V_{IL}}{-I_{IL}} = \frac{0.8 V}{0.4 mA} = 2 k\Omega\$

The lower limit is given by the current specification of the switch and your desired current consumption.

Note: As we now see, the presented circuit will not work for a LS-TTL input.

For a working pull-up, the resistor needs to generate a voltage drop of maximum 2.75 V for the maximum input current of 20 µA. So it has to be less than or equal to:

\$R_{PUmax} = \frac{V_{max}}{I_{max}} = \frac{V_{CC} - V_{IH}}{I_{IH}} = \frac{4.75 V - 2 V}{0.02 mA} = 137.5 k\Omega\$

Again, the lower limit is given by the current specification of the switch and your desired current consumption.

A look in the linked data sheet reveals a pull-up at each input, nominally \$20 k\Omega\$. This is one reason why you can omit a pull-up resistor with such TTL inputs, and why the input current \$I_{IL}\$ is so much higher than \$I_{IH}\$.

With another technique, HCMOS for example in the 74HC04, the input current is maximum \$\pm1{\mu}A\$. The calculation for the resistors is left as an exercise to the reader.

This answer omits other properties that are some times important. For example, clock inputs need a maximum rise/fall time. You need to take the capacitance on the input wire into account, inductive effects, and so on, especially in high-speed applications.