I tried to solve these errors using blind and buried vias, but the errors persist. I want when I repour the poly, it creates a clearance between the vias and poly. Or another solutions for the error. It is a 6-layer PCB.

Asked

Active

Viewed 33 times

1

-

You have pictured a thru (all layers) via, in net GND, which seems to connect to an inner layer (presumably GND as well). I don't see any blind or buried vias. Then, are you asking about the clearance and spokes (thermal relief) on the via pictured? I don't understand. – Tim Williams Jun 29 '23 at 23:33

-

VladimirVillamizar - Hi, You wrote an "answer" trying to reply to *JYelton*. That is not allowed on Stack Exchange. Answers should solve the original question, not reply to a person - therefore @ replies don't work in answers either, so your attempt to use that wouldn't have worked anyway. Please view the [tour] & [help] for the main site rules. || If you want to include an image in a *comment*, use [this](https://meta.stackexchange.com/q/310525) technique. Note that the draft answer (or question) *must not be submitted*. It is used only to upload the image & is then discarded. Thanks. – SamGibson Jun 30 '23 at 00:56

1 Answers

1

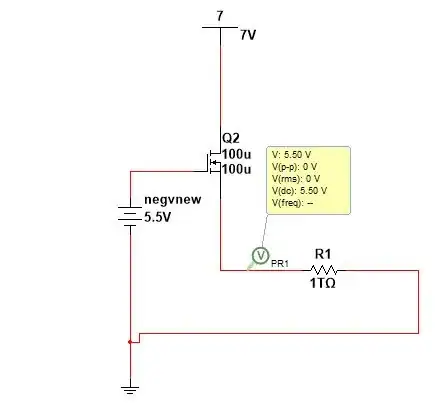

Use The a Clearance Design Rule for this.

Here you can specify a clearance (gap) between any two types of object (such as track and pad, or copper and via, etc.)

Don't forget to consult the official documentation on this.

JYelton

- 32,302

- 33

- 134

- 249

-

Can I use this tool only for the distance between the polygon and via? How? I tried and it is't work. Can you explain me? – Vladimir Villamizar Jun 29 '23 at 22:24

-

Ensure the polygon and the via are assigned different nets; the copper-to-via clearance defined should apply. If Altium is connecting them together, then either they are the same net, or some other condition not explained in your question is in effect. Have you re-poured _all_ polygons? After placing a via, any polygon touching it will need to be re-poured to create the clearance. – JYelton Jun 29 '23 at 22:45

-

In the image above the word copper is used in place of polygon.. Once changed and applied, all polygons must be repoured forthe change to take effect.@VladimirVillamizar – RussellH Jun 29 '23 at 23:17

-

-

@TimWilliams Perhaps, but the short-circuit errors I wouldn't think would result just from that. – JYelton Jun 30 '23 at 00:13

-

JYelton, you are right, I solve a lot of errors with your solution, but not all. – Vladimir Villamizar Jun 30 '23 at 00:21

-

@JYelton, So I solved a lot of error, but now I has a clearance constraint error. [Error screenshot](https://i.stack.imgur.com/bbIiE.png) I don't see the collision because, it is connected to her poly net. – Vladimir Villamizar Jun 30 '23 at 00:45

-

@VladimirVillamizar It is sounding like you have an unusual or non-default set of design rules. We cannot troubleshoot this problem in comments, but I'll give you this tip: Think of the clearance design rules as having two purposes. The first purpose is to govern how polygon pours are generated. If you specify a clearance of 0.2 mm from via to copper, then a polygon pour (when poured) will leave a gap of 0.2 mm from any vias that are not the same net. The second purpose is to generate DRC errors whenever that clearance is not met (violated), for you to review and correct. – JYelton Jun 30 '23 at 15:22