The crystal oscillator employs an inverter gate in the role of an analogue inverting amplifier, not a digital one. The gate on its own has a very non-linear input-to-output relationship, and inconveniently high gain. R104 provides negative feedback, which reduces gain, and improves linearity (and bandwidth), in the same way feedback resistance with an op-amp does. It just converts what was a digital gate into a better-behaved analogue amplifier.

The two capacitors C103 and C104 ensure that the crystal oscillates at its rated frequency. How they do this, and how you calculate their value, is a big topic, but you can read about it here. The crystal's documentation specifies a "load capacitance" \$C_L\$, and this value will decide the values of C103 and C104. In this schematic, the value of 220pF seems rather large.

C101 is the power supply filter capacitor. They way the schematic is drawn make it difficult to see its role, so I'll redraw a simplified version here:

simulate this circuit – Schematic created using CircuitLab

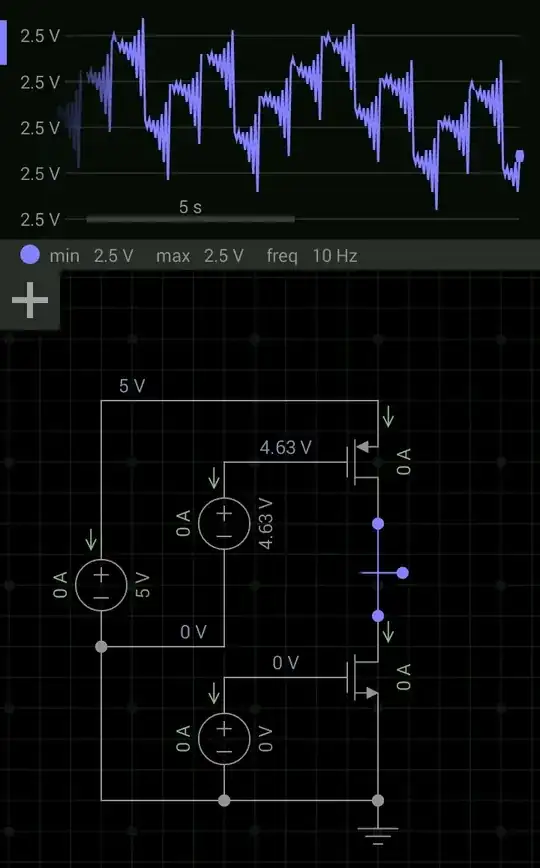

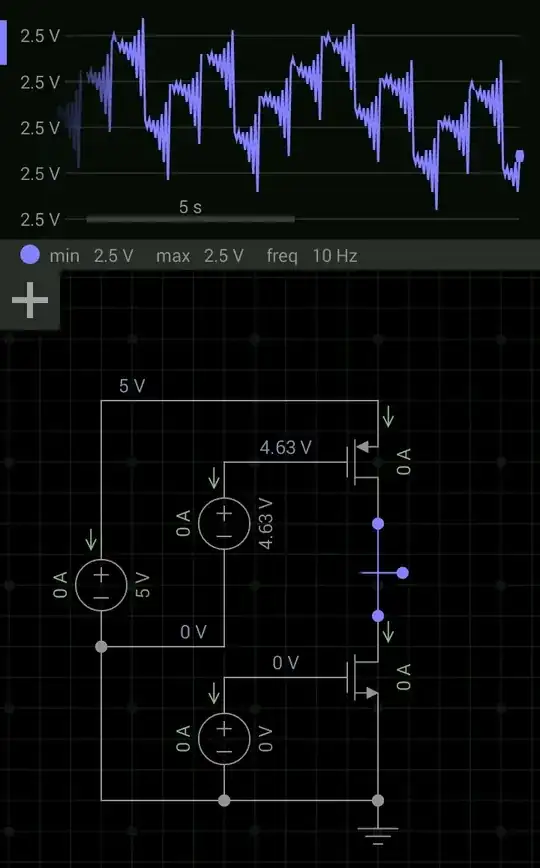

The diamond-shaped bridge rectifier represents the diode bridge formed by D101, D102, D103 and D104. If C101 were absent, the potential \$V_S\$ at the output of the rectifier (node S) would look like this:

This is just the full-wave rectified AC signal, with a frequency of 100Hz, which is clearly not good enough to power a DC circuit, so C101 is included to smooth it out, to a persistently high DC potential. With \$C_{101}=1000\mu F\$, and a load current \$I\approx 100mA\$, \$V_S\$ looks like this:

Capacitor C101 gets "topped up" with every peak of the rectified source, but slowly discharges between peaks, due to current being drawn by the load. The result is potential "ripple" at S. A larger value for C101 will produce less ripple, since it will discharge more slowly between peaks. A smaller value will cause it to discharge more quickly, causing the ripple to grow in amplitude. Here is \$V_S\$ when \$C_{101}=100\mu F\$, for the same load:

The designers have chosen \$C_{101}=1000\mu F\$ because this value produces an acceptable amount of ripple (which will be removed by regulator U101), given the current they expect this circuit to draw.

D110, D111 and R105 form an OR gate. Again, the way the schematic is drawn makes this difficult to see, so here they are drawn in a way that can be easily understood:

simulate this circuit

If either IC output goes high, the corresponding diode becomes forward biased, and pulls "1Hz" high. It is probably done this way to avoid the need for another IC containing an OR gate. This technique is called "Diode-OR".

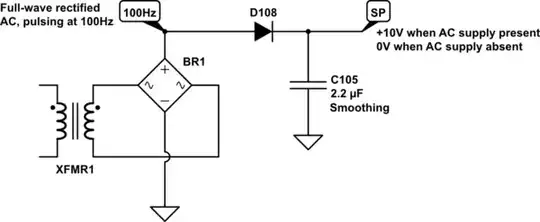

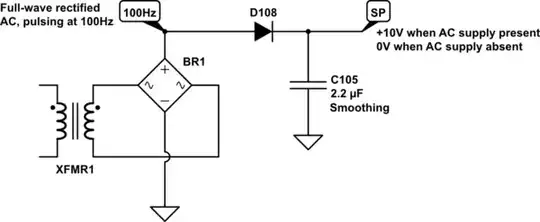

The other resistors and diodes you mentioned form small subsystems, which again have to be redrawn to be understood. Start with D108 and C105:

simulate this circuit

D108 and C105 form another small rectifier with smoothing capacitor. When AC is present, the "100Hz" node has the potential shown in the first graph above. C105 charges up to a steady +10V (approximately) on each incoming pulse. When AC goes away, C105 discharges, and SP falls to 0V. This is used as a signal to indicate the presence of AC power.

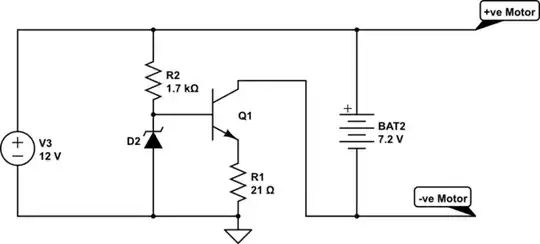

R102, R103 and D107:

simulate this circuit

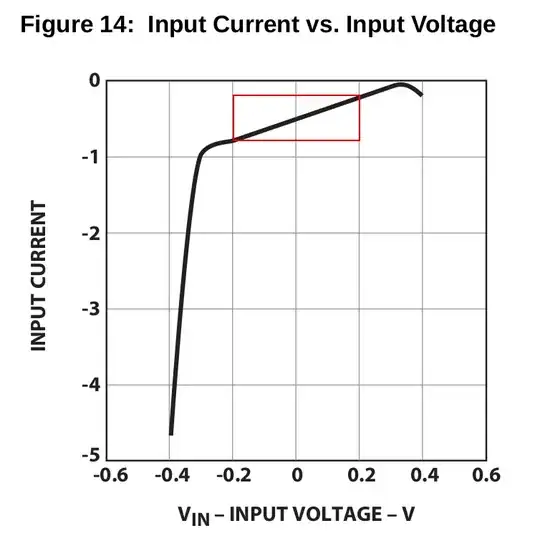

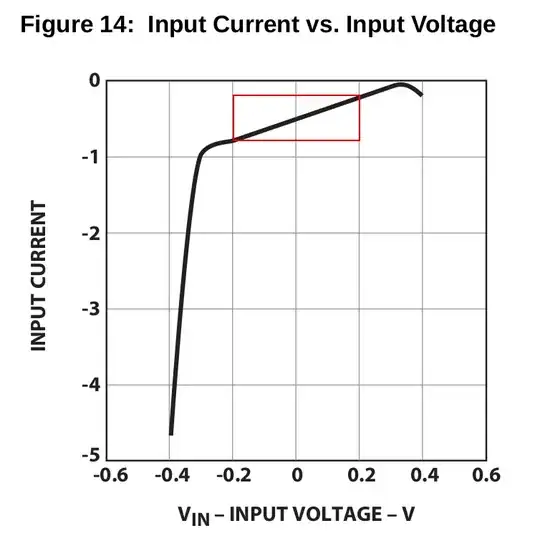

The 10V pulses at node "100Hz" cannot be directly applied to the input of U102, without damaging it. R102 and D107 together form a clamp, preventing the potential applied to U102 from rising above +4.7V. They convert a 10V signal into a roughly 5V signal compatible with U102. I am not sure what R103 is for, I believe the circuit would function perfectly without it.