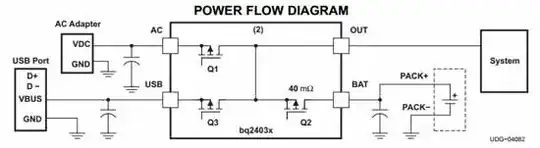

I am trying to simulate the LT8310 part in LTspice. Based on my understanding, this part can operate in either the current mode or the duty mode. I am interested in the current mode design. The block diagram of the part indicates that the VC (control pin) voltage level is set by the error amplifier between FBX and 1.6 V. There is an error amplifier between the amplified VSENSE voltage and the VC pin, which can reset the PWM control logic and adjust the duty cycle. Additionally, there is a parameter called RSET that needs to be modified since we are not using the duty cycle mode. This parameter sets the maximum duty cycle.

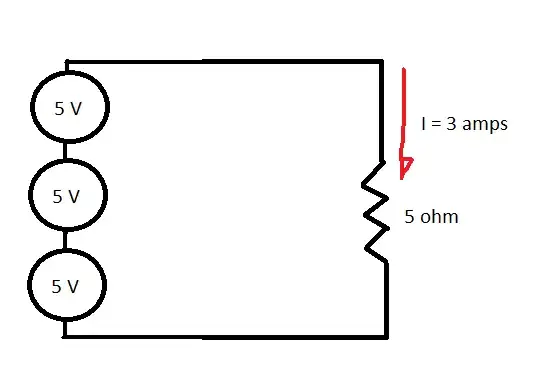

In my design, the input voltage is 24 V, the output voltage is 20 V, and the maximum current is 6 A. The frequency has been chosen as 400 kHz due to the use of an external clock. I have performed careful calculations, but I am encountering a negative value for the RSENSE current. I have estimated a value of approximately 6000 pF for C_RST, but it results in a VSENSE greater than 125 mV. If I make it smaller, it solves this issue but still negative ISENSE current. I would appreciate it if someone could identify which parameter is causing this issue so that I can further investigate.

In my design, the input voltage is 24 V, the output voltage is 20 V, and the maximum current is 6 A. The frequency has been chosen as 400 kHz due to the use of an external clock. I have performed careful calculations, but I am encountering a negative value for the RSENSE current. I have estimated a value of approximately 6000 pF for C_RST, but it results in a VSENSE greater than 125 mV. If I make it smaller, it solves this issue but still negative ISENSE current. I would appreciate it if someone could identify which parameter is causing this issue so that I can further investigate.

UPDATED

I have updated the post with the input I have received, but the issue in my simulation still persists. I have included the steps I have taken.

UPDATED

I have updated the post with the input I have received, but the issue in my simulation still persists. I have included the steps I have taken.

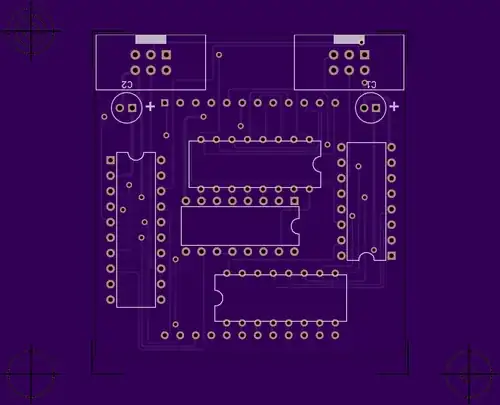

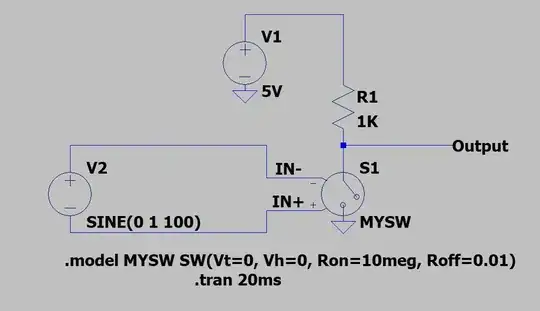

This is the updated simulation:

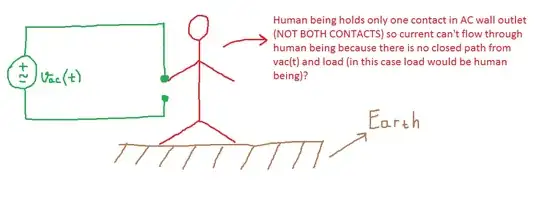

Still, the same issue persists. Although I can understand the concepts of magnetizing inductance (self-inductance) and primary inductance (coupled inductance) in theory, I am uncertain if I have modeled them correctly in LTspice.