I am looking at an FSM example in a digital design literature book where the idea is to create a simple FSM using a Moore machine for a Manchester encoder.

The FSM takes two inputs. d is the data signal, and v is the data valid signal. d is the signal to be encoded. The output of the FSM is y, the encoded result. The book doesn't specify any relationship between the clock generating the input signal d and the one clk driving the FSM. But, it mentions that the max speed that can be achieved is half the speed of the clock driving d, which is expected. It takes a transition from one level to another (d0 -> d1) to generate one output data (y0).

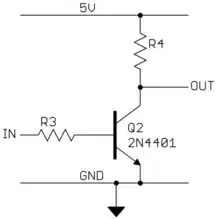

The state diagram suggested by the book is the following.

Notations: d' <=> (d = '0') and d <=> (d = '1'). Same for v.

The book doesn't explain how the states were derived and what they represent. This is an extract of the text.

I don't understand why the output y is asserted in the s0b state. If d is initially low, the FSM goes to s0a state. At that point, the next state is set to s0b regardless of the input, and the output y is asserted (y <= '1'). But, is this correct? The output should be 0 since we start from d=0 (a transition from low to high). (Update The reason of my confusion here, is that I was trying to solve a different problem. I was making a state diagram for a Decoder.)

I simulated the code implementing this state diagram and I see a strange behaviour in the output y.

library ieee;

use ieee.std_logic_1164.all;

entity manchester_encoder is

port (

clk, reset : in std_logic;

v, d : in std_logic;

y : out std_logic

);

end manchester_encoder;

architecture moore_arch of manchester_encoder is

type state_type is (idle, s0a, s0b, s1a, s1b);

signal state_reg, state_next : state_type;

begin

-- state register

process (clk, reset)

begin

if (reset = '0') then

state_reg <= idle;

elsif (clk'event and clk = '1') then

state_reg <= state_next;

end if;

end process;

-- next-state logic

process (state_reg, v, d)

begin

case state_reg is

when idle =>

if v = '0' then

state_next <= idle;

else

if d = '0' then

state_next <= s0a;

else

state_next <= s1a;

end if;

end if;

when s0a =>

state_next <= s0b;

when s1a =>

state_next <= s1b;

when s0b =>

if v = '0' then

state_next <= idle;

else

if d = '0' then

state_next <= s0a;

else

state_next <= s1a;

end if;

end if;

when s1b =>

if v = '0' then

state_next <= idle;

else

if d = '0' then

state_next <= s0a;

else

state_next <= s1a;

end if;

end if;

end case;

end process;

-- Moore output logic

y <= '1' when state_reg = s1a or state_reg = s0b else

'0';

end moore_arch;

As expected, the waveforms show that y is asserted erroneously following a transition from 0 to 1 in the input signal d. I am starting to believe that this state diagram is incorrect. Can someone help me figure this out?

Another concern is how to define an FSM clock that allows to sample the transitions of the d correctly as they come.

Update

I re-simulated the DUT using the suggested tips. The waveforms behaves correctly.