I managed to run an M.2 SSD (Samsung PM991A) in a TypeE socket with an adapter designed by CRImier (thank you):

I wish to design my own board with similar functionality, and I can't understand one thing with this desing.

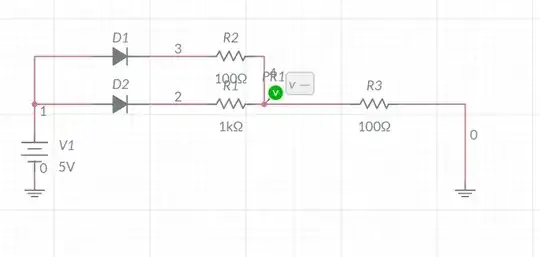

Here is the schematics:

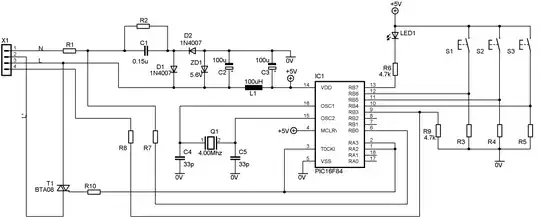

Here are two pinout guides:

- https://www.congatec.com/fileadmin/user_upload/Documents/Application_Notes/AN43_M.2_Pinout_Descriptions_and_Reference_Designs.pdf

- https://pinoutguide.com/HD/M.2_NGFF_connector_pinout.shtml

The socket seems good on the schematic, however the card pins are not. Based on these above two pinout guides (for KeyE):

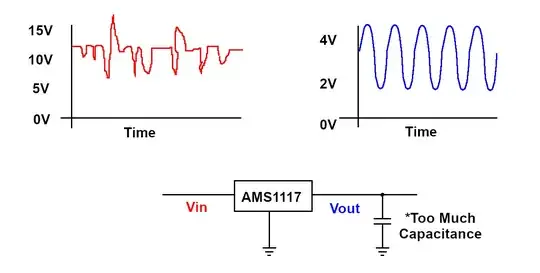

It seems the schematic is mixing up the transmit and receive pairs. Or we have to swap these when designing a card (instead of socket)?

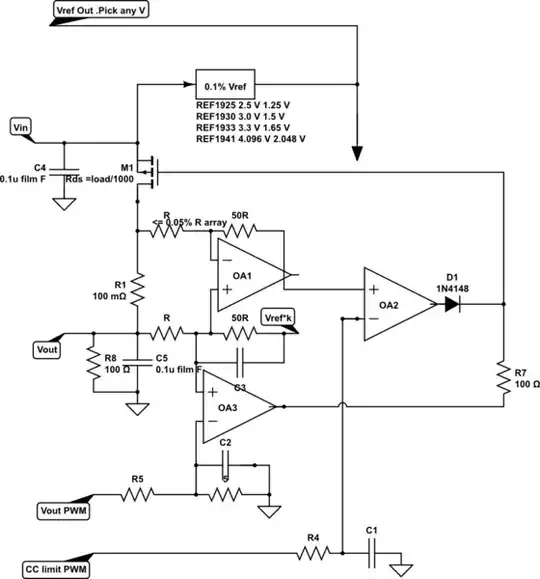

Another weird thing is this:

Even if we consider swapping TX and RX a mistake: one is connected straight, and other is crossed. Is this legal?

The only sane reason I found is this way he didn't need to use vias for these wires:

As this adapter is working correctly, I really wish to understand the reasons behind these swaps of RX<->TX and straight<->cross wiring.