I use FSMC in STM32F407 to access external SRAM IS62WV51216. I read RM0090 and AN2784, gives me two fomula

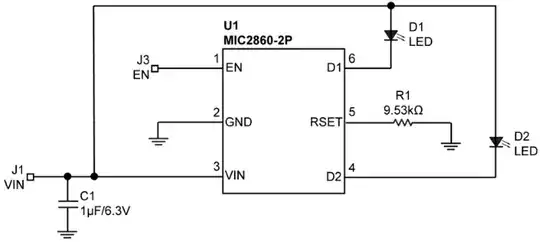

here is the SRAM reading timing graph

here is write timing graph

here is write timing graph

1.why WE have two falling edges on the left

2.what dose tSU tV mean,where is it in the timing graph, please draw it on the timing graph. My ENglish is not good and I have some issues on reading, I don`t understand "Data to FSMC_NEx high setup time + FSMC_NEx low to FSMC_A valid".I think the latter contain the former. It is conflict.

3.Where is ADDSET and DATAST in STM32 parallal in SRAM timing graph, how to calculate ADDSET and DATAST, I really nead your help.