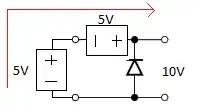

You are driving your p-channel MOSFET incorrectly

To drive it correctly, the input activation voltage must take the gate 5 volts (or more) below the source voltage. Then, return it to the source voltage when deactivating the MOSFET.

You currently have the activation voltage connected to 0 volts and that means that as the source voltage gets lower, the true activation voltage for the MOSFET gets lower. If the source voltage became zero volts then there is no possibility of the MOSFET activating.

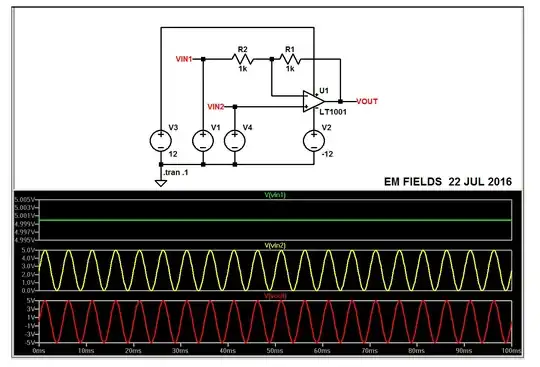

However, due to the gate-drain capacitance, there will always be spikes transmitted from gate to drain when the input waveform has fast rise and fall times (high positive and negative slew rate).