In the earlier days of the 7400 series devices (when they were just being rolled out in volume to the hoi polloi), they were limited to just a few transistors and resistors within the IC device. These later became called SSI (small scale integration) when more sophisticated devices came along. But early-on, all we had were SSI to work with and we didn't call them SSI -- not at first, anyway.

At the time, it was more about just providing the basics with which interesting projects could be realized. This meant a focus on exactly and only what was actually needed and very little duplication, if the purpose could be otherwise served by already existing ICs.

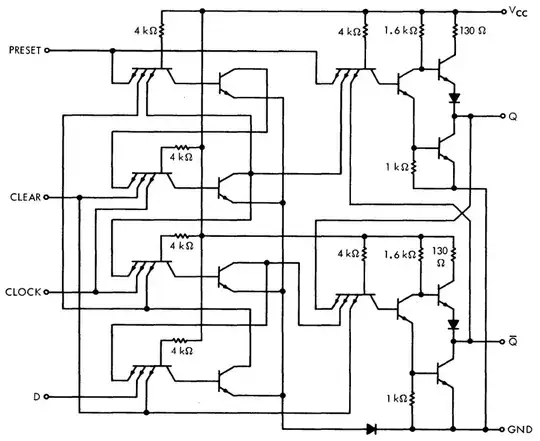

There was no tri-state, at first. This would have required a bunch of excess transistors to implement and there were certainly other priorities at the time. Also, there was the question of fanout (the ability of the output to source or sink current and the needs of the inputs into or out of which current was needed.) And finally, BJTs for these ICs were all essentially going to be NPN.

It was early recognized that there was a need to tie multiple outputs to a single bus. But again, there was no tri-state. That wasn't going to happen. Not at first. So NPN open-collector got elected here. This meant there would be two kinds of outputs: (1) always driving and able to either source or sink current; and, (2) open-collector and only able to sink current (lots of it, hopefully -- see 7406 and 7407, for example) but not source it.

Gradually, we saw MSI and even LSI appear.

An example of a memory device was the 7489. Here, a bus is definitely needed and open-collector was really the only method available. A simple NPN, laid out big on the IC so they could sink a fair bit of current, was added to the internal logic to drive the pins on the IC. They were not going to go add two BJTs (or more) just to get the logic to be convenient for you. These BJTs cost space and money. So the 7489's output was the inverse of the latched inputs.

(The 74189 came out later on.)

Also, note that in order to drive an LED (common desire back then), it could not be driven by the active high of a regular TTL output. Only an active low of an open-collector output, and only for certain of the ICs which had the blessing of a high-current output sink capability, could handle it. But this, of course, meant that an output low is what turned the LED ON. People being people, they wanted to see an LED lit up when the data was a "1", not a "0". To keep the circuitry minimal, this often meant that a low output should reflect a "1" input. And that's exactly what it did do with the 7489, for example.

Certainly, as time progressed and more 7400 series devices were developed, there were more options. Tri-state came a long, for example. And a lot more MSI and even some LSI started appearing.

No one owned a working crystal ball at the time. They could just see what was immediately in front of them. They certainly couldn't anticipate what people 50 years later would wonder about, nor design things at the time so that people in the 50 year future would say "that all makes sense." They just dealt the cards as they had them.

Just put yourself in their shoes for a moment and it will all make a lot of sense, then.