Problems with your code

temp_result <= temp_result mod divisor;

That's a bad idea: integer mod is an immensely complex operation.

Unless divisor is a power of 2, the combinatorial approach to modulo will be nearly as complex as doing a division.

divisor <= divisor / 4d"10";

same problem; dividing by 10 needs a relatively complex divider with a large combinatorial depth.

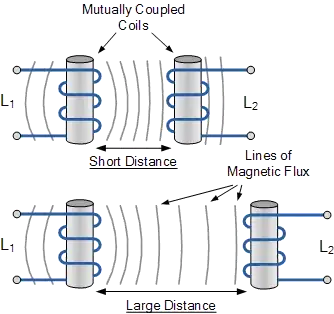

Complexities of integer mod and division

Here's a slightly dated view of the combinatorial implementation of division in yosys targetting a small-cell FPGA (from an older answer of mine):

(Divide on an ICE40) (warning: ~100 Mpixel image)

So, in general, doing division or mod just in a combinatorial path like you do here is a pretty bad idea.

You'll want to implement a pipelined modulo, I'd guess. Depending of the relative lengths of temp_result and divisor, that can be relatively flat, or deep.

Ways out

Well, you'll notice

- there's probably quite some overlap between what you need to do to calculate

a mod b and to calculate a / b.

- there's no easy way out – division is just combinatorial intense. So, we need to trade slack for pipeline depth.

The 2. issue is something you'll be quite familiar with when you look what time it takes for anything but really number-crunching optimized CPUs to divide integers – many processor instruction sets do have some kind of integer divide and integer modulo operations, but they take multiple, often many, clock cycles to complete.

So, I'd try to find an existing implementation of pipelined integer division (mod is often a side product of that) (for example, on opencores.org), or write a very naive one myself, which doesn't need to have constant throughput.