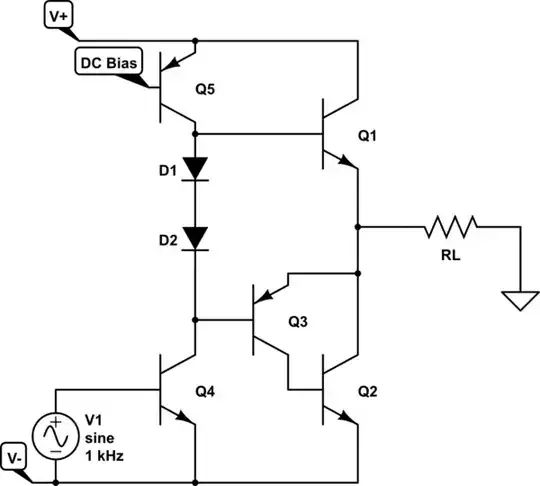

Sadly, 16V is not high enough, but neither is 0V low enough for Q3's gate.

Q1 is supposed to drive Q3's gate high, but its base-emitter junction drops 0.7V (it's operating as an emitter follower, don't forget), leaving only 15.3V at the gate, for \$V_{GS} = 3.3V\$. Q3 could require \$V_{GS}=4V\$ to just begin switching on. To switch it on and pass significant channel current (without dropping significant voltage between drain and source), I expect you'll need much more than 16V at its gate.

Fig. 1 on page 3 of this datsheet shows you what voltage \$V_{DS}\$ you can expected the channel to have at various \$V_{GS}\$ and channel currents. For instance, looking at the curve for \$V_{GS}=4.5V\$, you can see that at 3A channel current, you lose 0.4V. I think you should be aiming for \$V_{GS}=6V\$ at least for this application, which implies a gate potential of 18V.

The worst issue you will face is that by using an N-channel MOSFET high-side, you are operating it common-drain, as a source follower, whose source is never further than 4V below the gate; \$V_S = V_G-4V\$. You bring the gate down to +0.7V (not 0V, again because Q2 is an emitter follower), and Q3's source gets clamped to a minimum of -3.3V. This is bad, since the source (cathode of D1) must be free to swing to -12V in order to charge C1.

You must therefore drive Q3's gate with potentials +18V and -8V or so, which is quite the dilemma. The NMOS solution in the answer by "Kuba hasn't forgotten Monica" can be simulated; watch how gate potential swings between these extremes. The easiest solution to both of these problems is to use a P-channel device, which you can switch with 0.7V and +11.3V.

Update: I made it sound like PMOS answers all the problems, but be aware that in this setup it's easy to get \$V_{GS}\$ to exceed ±20V, which is a common maximum for many MOSFETS. Either make sure you use a device which can handle ±24V between gate and source, or take measures to protect that gate.