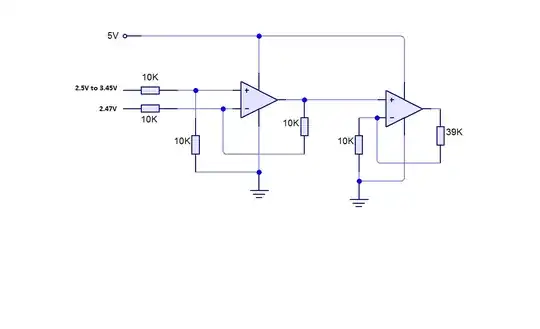

The wording in the manual is a bit odd, "isolating ground metal", which might be better phrased as "grounded copper".

In effect, the manual is saying to ensure that as far as possible, between the clock and any power rails, there is some grounded copper in between. This will ensure any capacitive coupling is between the xtal and the ground, not the xtal and the rail to reduce if not remove the possibility of the clock leaking onto the power rail. Similarly, it will ensure the power rails don't "detune the Xtal" ie negatively affect it, presumably either through capacitive or resistive coupling.

You might use a similar sort of thing in various scenarios, sometimes even the Mega Ohm resistive paths that can be present on a circuit board can cause problems, so you make sure the ground encircles the sensitive net.

In your specific example, replace the keep-out zone, so it excludes traces but allows the ground pour. Or personally, I would just make a note, perhaps even a colored box on a non-technical layer to remind me. Obviously, your current design rules will prevent copper between pads 8 and 9 of the chip, but you could still shift the Xtal a bit to the left to allow the ground pour to run right up to the pads. Currently, there's no ground between XTAL_0 and VDO_DIG, which is the opposite of what the manual is asking for.

[edit] I missed your update while typing my answer. The second image, while it does get the ground net all the way around the Xtal, is a poor choice as it forces the return current through a choke. You can just use one ground pour, you don't need the gap.