While I can't say when issues will happen, in a practical sense, I can tell you what is recommended.

Phillips, the i2c creator, recommends a SDA VDD VSS SCL pinout on cable for that very reason.

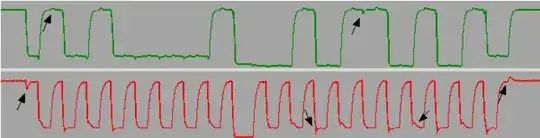

The reason for unusual arrangement of the power lines being between the I2C wires is to stop crosstalk. ie the edges of SDA and SCL coupling together. Placing VDD and GND between SDA and SCL, means that the capacitance on either signal line is equal (for 4 wire cable)

This is the Philips recommendation. The pattern is that set out in section 17.3 of The I2C Bus Specification. (There are recommendations for twisted pair as well)

If the length of the bus lines exceeds 10 cm (ribbon cable or on pcbs)

This arrangement will have similar capactive loading on SDA and SCL.

Where you don't use pins 5 & 6, it can be better to just use 4 wires. For longer runs, use twist&flat ribbon, or split 5&6 from 1-4

Avoid bundled cable where the conductors aren't individually twisted pairs or individually screened

Emphasis mine. From the actual Specs (Section 17.3):

These wiring patterns also result in identical capacitive loads for the SDA and SCL lines. The VSS and VDD lines can be omitted if a PCB with a VSS and/or VDD layer is used.

If the bus lines are twisted-pairs, each bus line must be twisted with a VSS return. Alternatively, the SCL line can be twisted with a VSS return, and the SDA line twisted with a VDD return. In the latter case, capacitors must be used to decouple the VDD line to the VSS line at both ends of the twisted pairs.

If the bus lines are shielded (shield connected to VSS), interference will be minimized. However, the shielded cable must have low capacitive coupling between the SDA and SCL lines to minimize crosstalk.

Having a ground plane (or vcc plane) below the traces is enough, according to NXP/Phillips.

Now, to be honest, I currently use a 10 INCH (25 cm) cable, with SDA/SCL twisted together, and separately, VCC and Gnd. Works fine at the 125khz speed I am using, no errors or nacks, and I'm pretty much doing the opposite of what it says I should do. While the 17.3 section does not mention as this being only for 400khz or 1000khz speeds, it seems to be very very cautious.