We are evaluating MIC21LV32 from microchip in one of our applications.

For the current sensing we have used 3 mΩ sense resistor (1206, 1 %, 1 W), as these sense resistors have higher ESL+ parasitic inductance in PCB. During testing with R1=R3=100 Ω, No C2, C3, C4, we are seeing large spikes on CSP-CSN nodes.

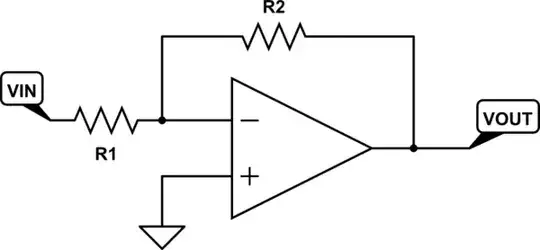

My question is, for the current sense filter circuit (R1, R3, C2, C3, C4) below,

how can I decide the values of Input filter components (R1, R3, C2, C3, C4) so, that I can get clean voltage across 3 mΩ resistor alone even though ESL present.

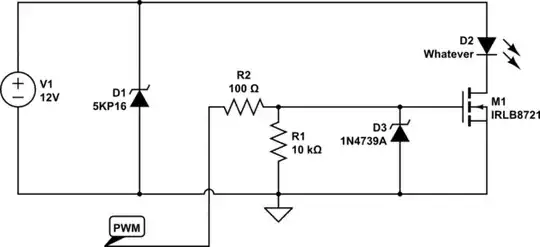

Below is the simulated circuit.

Below is the response of the circuit.

I have chosen common mode filter values (R1, R3, C3, C4) in schematic, differential mode filter values (R1, R3, C2) randomly.

With same values I have done testing, but I do not see such improvement in the captured waveforms. Simulation to actual HW only difference is AGND & DGND are connected at one place (near thermal pad), I simulation I have shorted it directly.

How can I go systematically to improve the response of the circuit?

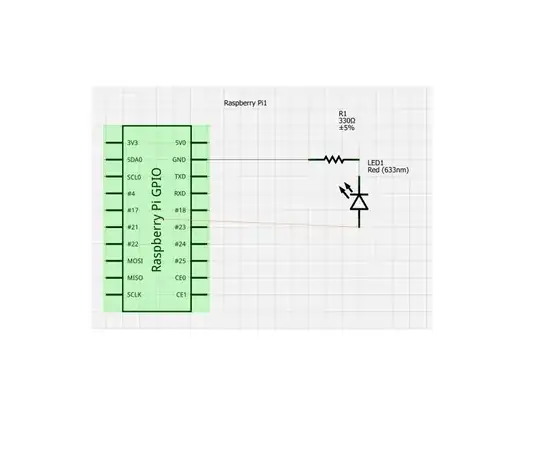

Adding capture with both resistors are 100 Ω, no capacitors are mounted.

Top waveform is Math - which is CSP-CSN/3mE.