I recently asked a question on why my naive implementation of a XOR circuit in CMOS was wrong.

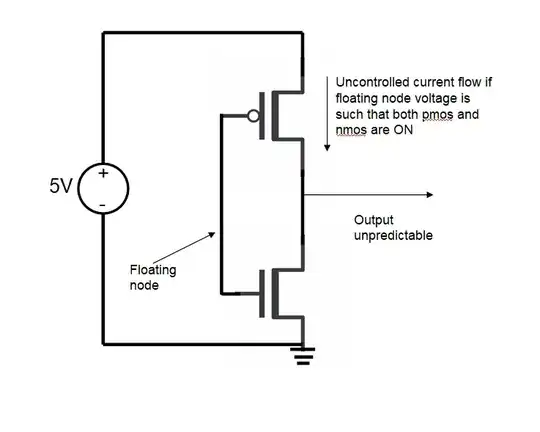

One of the most mentioned issues was that I had a floating node in my diagram. I've looked up floating nodes, and I understand the idea that they're signal lines without a well-defined voltage. I'm also aware that this can cause erratic behaviour in a circuit. However, I can't find any examples of what strange behaviour this causes.

What are some common issues that floating nodes cause?