I have been using the Integrated Logic Analyser (ILA) on Vivado 2021.2 to log some signals from a RISC-V processor running on an FPGA (BASYS 3 FPGA development board).

The signals I am monitoring are all 32-bit lines of a register, the reset signal of the processor and the 100MHz clock that the RISC-V core is running from. My problem is that when I arm the trigger for the ILA, activate the trigger and view the signals, the clock input is always shown as 0, even though the register lines and reset signal change as expected. Why could this be? Below I have a detailed description of what the setup and what else I have tried:

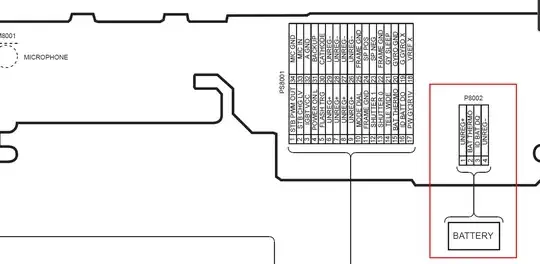

So the clock on the FPGA is 100MHz and it is used to clock the RISC-V core as well as drive the clock for the ILA. The reset signal for the RISC-V core is active low and setup as trigger only on probe 0. Clock signal is data only on probe 1 and the register is also data only on probe 2, like below:

component ila_0 IS

PORT (

clk : IN STD_LOGIC;

probe0 : IN STD_LOGIC_VECTOR(0 DOWNTO 0); -- Reset signal

probe1 : IN STD_LOGIC_VECTOR(0 DOWNTO 0); -- 100MHz clock

probe2 : IN STD_LOGIC_VECTOR(31 DOWNTO 0) -- Register

);

END component;

And here is the ILA probe setups:

All the signals in the FPGA design are of type std_ulogic or std_ulogic_vector so as the ILA requires std_logic or std_logic_vector signal types, I have had to cast them like this below:

clk_i_100MHZ_ila(0) <= clk_100MHZ;

rstn_invert_ila(0) <= rstn_invert;

program_counter_ila <= To_StdLogicVector(program_counter);

And here are the signals connected to the ILA:

ila_instance : ila_0

port map(clk => clk_100MHZ,

probe0 => rstn_invert_ila,

probe1 => clk_i_100MHZ_ila,

probe2 => program_counter_ila

);

Here are the trigger and capture settings when online with ILA:

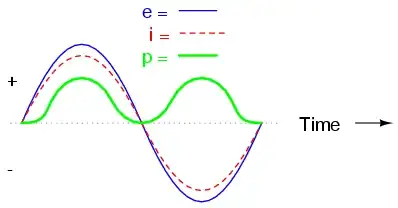

Below is what the ILA captures after I press the reset button on the board which resets the RISC-V core and is the trigger for ILA. You can see the reset signal is working as trigger (falling edge) and the other signal is changing, but the clock is always zero:

I thought that maybe the ILA and the RISC-V clocks being the same speed at 100MHz was the problem, so I changed the RISC-V clock to 80MHz and left the ILA clock at 100MHz (not shown in these images) but the problem still exists. Any ideas?

EDIT

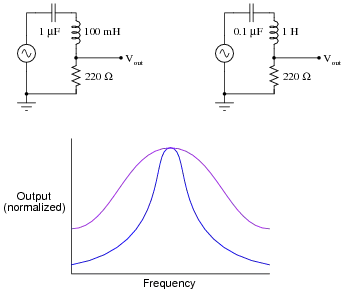

Ok so I have done some more research myself and found this:

The first response by avrumw seems to answer this question. It seems using the clock for non-clocking lines is always a bad idea and the frequency of the ILA probably needs to be much higher than the RISC-V clock rate to get any signal changes appear visible.