I think what’s confusing you is the notion that a logic ‘0’ represented as a zero-volts value is somehow ‘no signal’. It most definitely is: it’s a voltage that’s being held at 0V by something, referred to system GND. Sender and receiver agree on this shared understanding of '1' and '0' being referenced to GND.

A CMOS logic low is in fact a low-impedance connection to GND, not an open circuit. CMOS logic signals are explicity driven high or low by FETs.

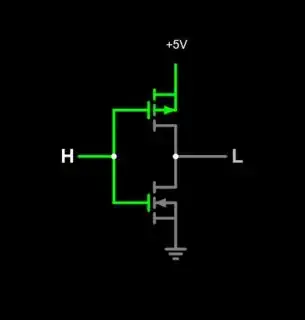

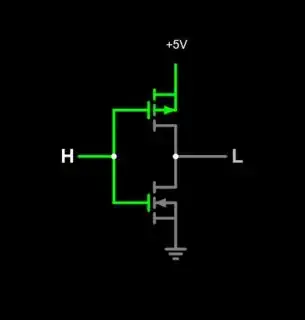

You can think of a CMOS output as a single-pole double-throw switch that ties the output either to GND or the power supply. The NOT gate is the simplest of these, with just the FET pair, doing its SPDT thing.

Here's a CMOS NOT gate you can try for yourself (simulate it here)

You can see the action of the FET pair, connecting the output to either +5V or GND depending on the input. To function, it needs both a power/GND connection, and an input signal that is referred to GND to guarantee correct voltage to the FET gates.

Other logic families are similar: the driver always guarantees a valid voltage level representing either a one or zero, referenced to GND. Their inputs are never left 'disconnected'.

NOTE: In some logic families, a disconnected input will assume a logic level. TTL for example will assume a '1' due to its diode-OR type input structure with a local pull-up. This is not recommended practice. You can explore this further in Falstad, which has examples of TTL, DTL, RTL and other gates (see Circuits/Logic Families.)

As you touched on, voltage isn’t the only way to represent logic. The absence or presence of light, or magnetic flux, or current, or sound, or some other physical phenomenon can also do this. As long as there is agreement between transmitter and receiver, logic levels can be sent reliably from one place to another.

When there isn't a shared voltage reference, some transmission methods instead encode 1’s and 0’s not as static signals, but as changes in some other signal. A primitive example of this would be frequency-shift keying, or FSK, where a carrier tone is frequency-modulated by a digital signal. FSK probably best known for its use in 300 baud modems.

A benefit of using FSK is that there is always a carrier present: the receiver knows that it has a link established with the transmitter, even when there is no data being sent (or, it's a run of zeroes.)

Similarly, the digital audio SP/DIF standard has both a wired (coax) and optical version (TOSlink.) TOSLink turns a LED on and off to send a binary stream down a fiber optic cable. But it sends something all the time: a clock combined with the data stream using a technique called differential Manchester (or biphase-mark) coding.

Thus, SP/DIF coax and TOSLink are always sending something, even if the data it is sending are all zeros (or, not valid). Again, like FSK, the coax or TOSLink receiver knows a link is present even if no data are being sent. There is a baseline established even without a physical ground connection (SP/DIF can, and often is, AC-coupled via isolation transformers, especially in its pro-audio AES version.)

Stepping back, understand that for valid transmission of data to take place, the sender and receiver have to have a shared understanding of not only what defines ‘1’ and ‘0’, but of a baseline reference for a link to be formed. For a local logic system that is usually the power supply reference. If no such reference exists between sender and receiver, it needs to be agreed upon in another way.