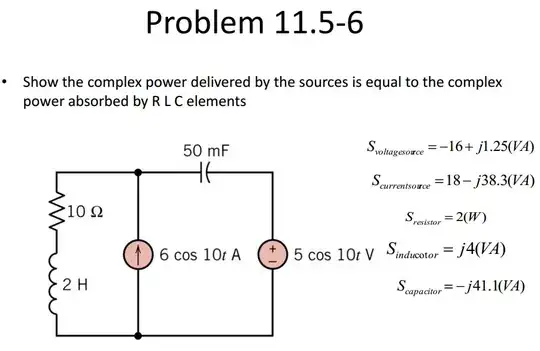

Summary / Question

I have this PCB (top only):

There is essentially no "signalling" happening here, and the only divergences from steady-state are when the input AC (T1) turns on or off, or when the right pair of pins of T3 are shorted (causing the relay K1 to engage and latch). State changes can be assumed to be separated by seconds, at minimum. See below for schematic and more information.

For the bottom, however, there are two obvious options.

I could just run traces:

Or I could pour a voltage plane:

In a "non-signalling" application such as this, what are the advantages and disadvantages of each of these approaches? (Or are they both dumb? What should I be doing instead?) Also, in the pour case, should I be maximizing the size of the pour (keeping in mind it can't be "the whole board" in order to stay far away from the high-voltage AC), or keeping it closer to the convex hull of pads to which it connects?

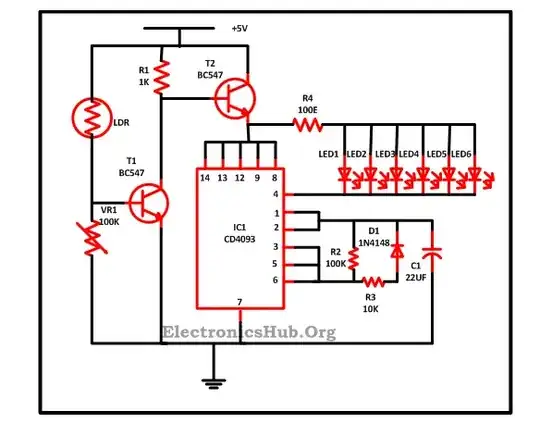

Details

This is a manual delay-start circuit. Here's the schematic:

(Pin assignments for T1, T2 and T3 are arbitrary and may be switched in the PCB as compared to the schematic based on whatever works best for the PCB layout.)

Main switching happens upstream on the AC side. The intended functions of this circuit are:

- Don't supply power to T2 until the user presses an additional button.

- Keep power to T2 shut off if power from T1 is interrupted.

- Illuminate an indicator when the T2 has power.

- Provide power (stepped down by R1, R2) to some fans.

On the PCB, the very left is the AC mains input and can mostly be ignored, aside from "keep clear of this area". The middle top also needs to be unpopulated (and may even turn into a cut-out) for mechanical reasons.

For the left ("switched") and middle (ground) nets, I am very deliberately shaping the path from both the (inductive) load and relay coils to go directly to D2 before going anywhere else, as D2's reason-to-exist is obviously to 'eat' voltage spikes from these when the power goes out. For that reason, and because of the several nets on top, I don't really want to try to fiddle with pours on top.

Please use chat for any questions or suggestions not related to the pour-or-traces question.