As a development to my previous question I am developing a protocol to drive VGA through lines originally designed for SPI communication.

The problem is that I may be able to instruct the receiving decoder to have either VSYNC, HSYNC or color. This means I can't perform HSYNC during VSYNC. To my understanding no RGB color information during HSYNC or VSYNC should not be a problem.

Searching for information I can't find any trustworthy source of info to decide if VSYNC without HSYNCs will work with all VGA monitors. Most sources compare HSYNC or VSYNC to picture/color frame, the only place I found something material is here.

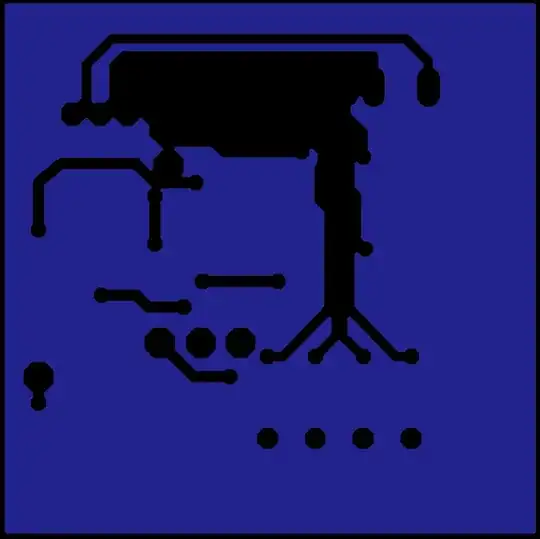

This clearly shows that there are HSYNC pulses during the VSYNC pulse, but there's no clue if it is someone's assumption that it always must be this way per specification. Referenced link to datasheet of ADV7125 does not help much.

I would expect there is no vital need for HSYNCs while VSYNC is in progress, but would love to see any trustworthy source confirming or disproving this assumption. Any help would be greatly appreciated.