I recently asked some questions for an application in hope to gain more clarity on how to accomplish an emulation of an input device peripheral (in my case an input mouse) in simulation. Following several attempts of debugging and simulation I actually accomplished a simulation of this peripheral. I am faced with with a question of feasibility. The controller is a design that will run on my FPGA board. The actual peripheral runs alongside the board but externally connected. At present the mouse does not reach proper state to communicate movement data to the FPGA.

I have considered that if I make the peripheral run inside the FPGA by making it as close to the scenario as possible I can figure out why I can not get the mouse to initialize properly outside.

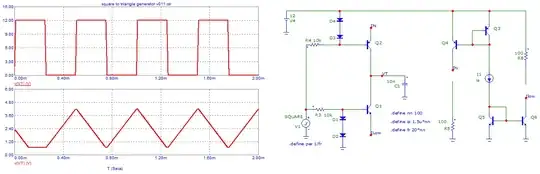

I do not have internal specifications of the actual mouse so I created my own description as best and as close to a PS/2 mouse as I could. I got the simulation to display mouse packets received by the controller on the simulation waveform.

I have refrained from posting the RTL code because it might add too much unnecessary information but if relevant parts are needed I can post them.

Questions

Is this approach of bringing the mouse closer to the design on chip by somehow mimicking behavior of the mouse feasible?

If so, can it be accomplished preserving the bidirectional nature of communication somehow on an FPGA?