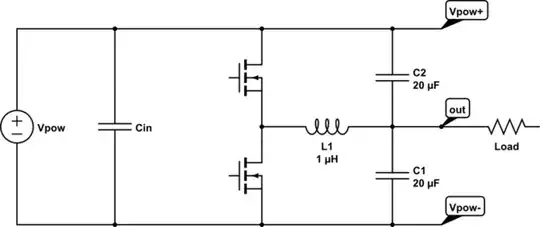

Please consider the simplified Class D output stage below. Depending on the half-bridge duty cycle, different output voltages (within the power supply range) can be applied to the load.

simulate this circuit – Schematic created using CircuitLab

The output filter is usually an LC filter like shown in the schematic. For all schematics that I have seen so far, the output capacitance is placed only in the position of C1, i.e. to the negative power rail. Now, for an application like a synchronous buck, that goes from 12 V to ~1 V that might be sensible because less bias will be present across C1 than across C2.

But when this topology is used to generate varying output voltages, both close to the positive or negative power rails (like e.g. in a Class D audio power stage), the DC bias of the output capacitors can change their effective value rather strongly for the case of usual X5R ceramics for example.

So I was wondering if one could distribute the output capacitance between C1 and C2 (i.e. to both power rails) to somewhat mitigate the effects of the DC bias on the total capacitance. Spice shows that the inductor ripple current nicely splits between both capacitors, so they are effectively in parallel for the ripple current. Is this a good practise to implement output capacitors ? It somehow doesn't look right to me.