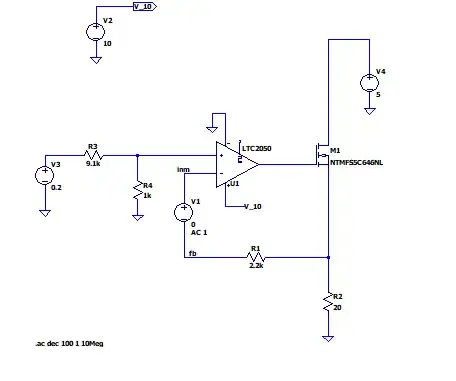

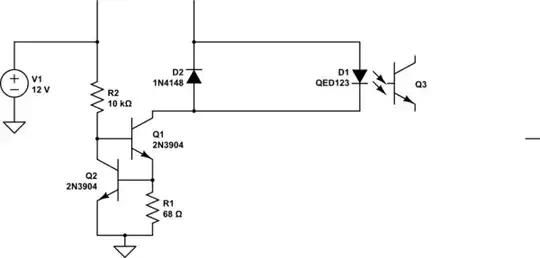

Short summary: V3 decides the current going through R2. If V3 is 0 V then no current is going through R2. If V3 is 10 V, it will be approximately 50 mA.

I want to do an open-loop simulation of this voltage-controlled current source.

The conventional method is to remove the DC current source (V3) and add a small signal analysis source at the feedback, and do an AC analysis frequency sweep of V(fb)/V(inm).

Nothing useful can be found using this simulation method. You need a DC operating point at the non-inverting input of LTC2050 (U1) for it to drive the nMOSFET gate (M1.) It seems like the minimum DC-operating point is 0.2 V.

I ended up with this simulation, and also a reasonable Bode plot:

The phase margin for this circuit is 56°, with a DC operating point (V3) of 0.2 V.

Now comes my question:

Should I simulate this open-loop simulation with different DC operating points or just select the minimum DC operating point? V3 will have a voltage that varies from 0 V to 10 V.