I need to design a circuit that has a gain of 0 dB that allows a voltage attack on a 100 Ω load.

My first thought was to make a common-drain circuit since I had to use only JFETs. First I only used 1 JFET resulting in a gain of -3.6 dB. To increase it, I connected JFETs in parallel, 4 exactly, to have a "super transistor" which improved my gain to -1.26 dB, but I am still quite far from the result. I could've added more but I want this circuit to be makeable without too many struggles. I tried to modify every single resistance and even added some, but -1.26 dB was my best result. This was my circuit:

The specifications needed:

- Input impedance of at least 1 kΩ

- Max. output impedance of 10 Ω

- Gain of 0 dB, so replicate the input signal.

- Power supply of +/-12 V

- Input signal is 2 V amplitude sine wave with 200 Hz to 5 kHz frequency

Any ideas on how to improve this?

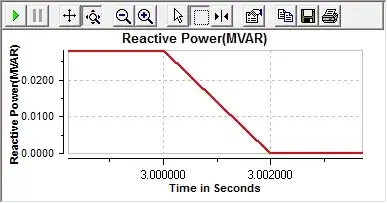

Here is the simulation:

PS: I know a 100 Ω load is ridiculous for a voltage attack because I will need an output impedance ≤ 10 Ω, but it is how it is.

Transient simulation at 2 kHz: