The four-FET ‘AND’ you show in your first diagram doesn’t provide proper gate bias for the FETs to switch correctly. It doesn’t really work.

More here: Why are the voltages the way they are in this transistor circuit?

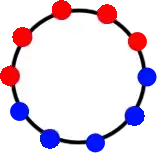

The second diagram, a NAND followed by an inverter, is standard: n-FETs used in the pull-down network and p-FETs in the pull-up.

I think this question comes from a misunderstanding of how FETs actually work, a detail that a typical logic-FET diagram like yours (bubble on gate for p-FET, no bubble for n-FET) tends to obscure.

What's not shown in either diagram is the source substrate connection. FETs turn on based on their gate-to-substrate voltage.

In the second (working) diagram then, the substrates connected as follows:

- n-FET source substrate is connected to GND or other low

- p-FET source substrate is connected to Vdd or other high

Following this rule ensures that the gate-source (substrate) voltages applied to the FETs are driving them fully on or fully off. Then you get the switch-like behavior you expect: logic '1' turns on the n-FET, logic 0 turns on the p-FET.