My goal is to be able to use a high-speed, low-distortion, BJT-input op-amp having a much lower input current - that's why I'm trying to JFET the inputs. I don't want to cut DC with input cap, I want the input current to be low. I want to use the JFE2140 from Texas Instruments.

I've found 2 useful articles:

- https://www.analog.com/media/en/analog-dialogue/volume-47/number-4/articles/tips-on-making-FETching-discrete-amplifier.pdf

- https://www.cordellaudio.com/JFETs/LSK489appnote.pdf

First article is about buffering the inputs. I'm stuck at the very beginning - finding a right buffer circuit. I don't know the reason why my source follower is saturating. For some reason this circuit clips; it's cutting the bottom part of the sinewave.

VCC is 15 V, VEE is -15 V, the current source is set to 5 mA (it's the optimal value for lowest noise according to datasheet). I need to handle 8 V peak without saturation. When I raise the current at I1 source to ~10 mA it's not clipping anymore, but the problem is that the power dissipation is becoming high, and this particular JFET (JFE2140) should work with lower Ids current I guess.

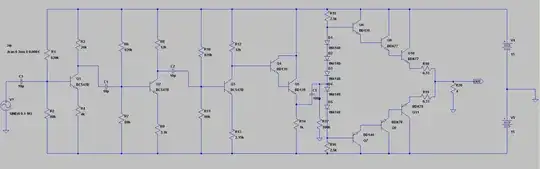

After raising I1 to 10 mA I get 0.008253% of THD - that's also too high, I need it 2 orders lower (more like 0.00008% - I get this figure with the op-amp alone). I also tried a hybrid solution (a source follower with a BJT buffer) but it didn't help much. Maybe it didn't help because I'm doing something wrong. Here is the hybrid solution:

When using simple input buffering I dramatically raise the distortion of the circuit. There is a second solution - a differential pair with some voltage gain working in the common feedback loop with the op-amp. When using this solution I can come to a point when distortion is really low, but it strongly depends on the gain setting resistors (marked with red on the picture).

Changing the resistors to set the gain to another value ruins the distortion performance and I must set the operating point again. I want this circuit to work right with various gain settings - from a gain of 1 (buffer) to a gain of, let's say, 10.

Any thoughts on that? Would you choose input buffering or the diff. pair solution? How can I achieve the same, low THD figure with all the gain settings while keeping the JFETs at a fixed operating point? And back to the basic question - why is my simple buffer saturating?